Data Speaking: Comparing 5 mainstream 10MHz OCXOs, which one is more suitable for your project?

2026-01-31 10:43:07

0

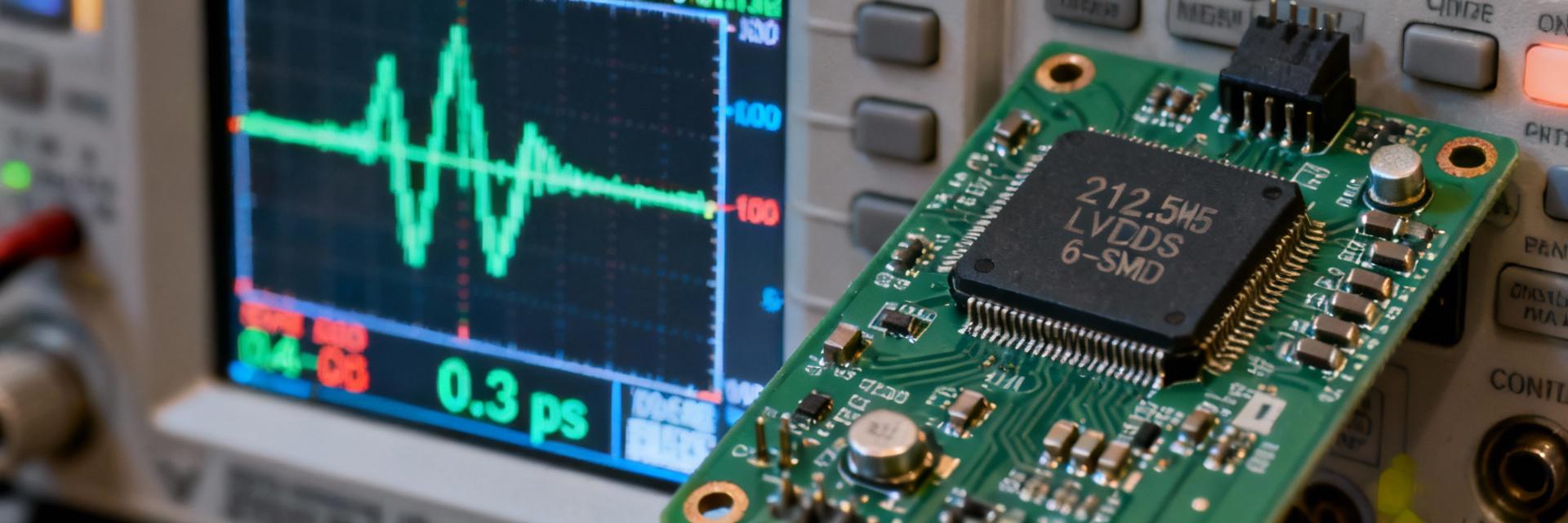

In the fields of precision timing, communication base stations, and high-end test instruments, the 10MHz Oven Controlled Crystal Oscillator (OCXO) is the core "heart" that determines system performance. Facing numerous choices on the market ranging from general-purpose to ultra-high-performance types, engineers often struggle between "parameter-first" or "cost-priority." This article will analyze the technical characteristics and application scenarios of five mainstream 10MHz OCXO types through a horizontal data comparison of key performance parameters, helping you make the most suitable data-driven choice for your project requirements. 01 Core Parameter Interpretation: How to Read an OCXO Datasheet? The first step in choosing an OCXO is understanding its technical specifications. Frequency stability, phase noise, aging rate, and power consumption are the four core parameters that together define the performance boundaries and application potential of the oscillator. Frequency Stability vs. Phase Noise Frequency stability measures the degree to which the oscillator's output frequency changes with environmental factors such as temperature and voltage, usually expressed in ppb (parts per billion). For systems requiring a long-term stable clock reference, such as communication base station synchronization, this is the primary consideration. Phase noise describes short-term frequency stability, representing the spectral purity of the signal, which is critical for the performance of RF systems, radars, and high-speed data converters. The two have different focuses, and a balance must be struck based on the "long-term stability" or "short-term stability" requirements of the application scenario. Aging Rate and Power Consumption The aging rate refers to the slow, unidirectional drift of the oscillator's frequency over time, usually measured in ppb/day or ppb/year. A low aging rate is key to ensuring long-term (multi-year) stable operation of the system, especially suitable for metrology and timing systems. Power consumption is directly related to the system's thermal design and power supply solution, particularly for portable or battery-powered equipment. High-performance OCXOs often require higher heating power to maintain the oven temperature, so a balance point must be found between extreme stability and energy efficiency. Horizontal Data Comparison of 5 Mainstream 10MHz OCXO Types OCXO Type Frequency Stability (ppb) Daily Aging Rate (ppb) Phase Noise (10Hz) Power Consumption (W) Economical General-Purpose ±50 ~ ±100 ~ 1.0 -130 dBc/Hz 1.5 - 2.5 Low Power Compact ±100 ~ 2.0 -125 dBc/Hz < 0.6 High Stability ±10 ~ ±20 < 0.5 -140 dBc/Hz 2.0 - 3.5 Ultra-Low Phase Noise ±50 ~ 1.0 -145 ~ -155 dBc/Hz 3.0 - 5.0 Ultra-High Precision < ±1 (sub-ppb) < 0.1 -140 dBc/Hz 5.0+ Economical General-Purpose: Best Cost Solution Suitable for cost-sensitive industrial control, general test equipment, and other scenarios requiring better performance than a TCXO. Low Power Compact: Preferred for Portable Devices Aimed at IoT terminals and portable instruments, reducing power consumption to the level of hundreds of milliwatts with extremely small package sizes. High Stability: Harsh Environment Applications Widely used in satellite communications, high-end spectrum analyzers, and systems requiring long-term timekeeping capabilities. Ultra-Low Phase Noise: RF Core Offers excellent performance at close-in carrier offsets, significantly improving system signal-to-noise ratio and bit error rate. From Parameters to Application: Typical Project Selection Guide 01 Scenario 1: 5G Base Station Synchronization and Broadcasting Equipment 5G networks have strict requirements for time synchronization to satisfy TDD modes and Coordinated Multi-Point (CoMP) transmission. Such projects typically require high stability OCXOs to ensure time errors between base stations are within hundreds of nanoseconds. Simultaneously, phase noise performance must be monitored to guarantee RF signal quality. Broadcasting equipment also relies on high-stability clocks to avoid signal interference. 02 Scenario 2: Portable Spectrum Analysis and Field Test Equipment These devices need to maintain sufficient measurement accuracy in mobile and outdoor environments. Low power compact OCXOs are the preferred choice, as they provide better stability than TCXOs while effectively controlling the overall power consumption and heat generation, extending battery life, and reducing device volume. 03 Scenario 3: Financial Trading Systems and Data Center Clocks High-frequency trading requires timestamp accuracy at the microsecond or even nanosecond level, and distributed systems in data centers also require precise clock synchronization. It is recommended to use high stability or ultra-low phase noise OCXOs to ensure absolute accuracy of time markers and clock consistency within the network, reducing trading conflicts and data synchronization errors. Beyond the Datasheet: Hidden Costs and Risks in Selection Supply Chain Stability and Lead Times For mass production projects, the OCXO supplier's capacity, lead times, and long-term supply commitment are crucial. Preference should be given to manufacturers with stable wafer and packaging supply chains, and second-source plans should be evaluated to avoid supply disruption risks. The Necessity of Upgrading from TCXO to OCXO This is not just a leap in performance, but also means an increase in cost, power consumption, and volume. Before making a decision, it is necessary to quantify whether the system-level benefits brought by performance improvements (such as improved communication quality and enhanced measurement accuracy) are sufficient to cover the increased total lifecycle cost. Future Trends and Procurement Action Checklist Currently, by improving heater design, adopting new thermal insulation materials, and MEMS crystal technology, the industry is launching OCXO products with smaller sizes, shorter thermal start-up times, and lower power consumption. This allows OCXOs to enter more application spaces previously dominated by TCXOs. Four-Step Selection Method Step 1 Define hard indicators for project stability, phase noise, power consumption, size, and cost. Step 2 Screen 2-3 candidate models based on requirements and perform detailed parameter comparison. Step 3 Comprehensively evaluate the technical support capabilities, quality systems, and supply chain strength of potential suppliers. Step 4 Be sure to conduct actual sample testing to verify long-term stability and adaptability in real application environments. Key Summary ● Parameters are the foundation, application is the yardstick: When choosing a 10MHz OCXO, core parameters must be closely integrated with the priority of specific application scenarios (such as 5G synchronization, portable instruments, metrology research) to avoid over-design. ● Five mainstream types, each with its own role: The market is mainly divided into economical general-purpose, low power compact, high stability, ultra-low phase noise, and ultra-high precision, meeting different needs from industry to top-tier scientific research. ● Evaluate hidden costs and future trends: Consider supply chain risks and technical upgrade paths, and pay attention to progress in miniaturization and low-power technologies. Frequently Asked Questions How to balance OCXO performance and cost in budget-constrained projects? + First, accurately evaluate the minimum performance baseline the project must achieve. Among models that meet this baseline, choose the most cost-optimal solution, which is usually an economical general-purpose OCXO. Consider sacrificing some non-critical indicators (such as choosing a model with a narrower operating temperature range) to reduce costs. Also evaluate the total lifecycle cost; sometimes a slightly higher initial investment is more economical due to a lower failure rate. Which is more important for communication base station projects: phase noise or frequency stability? + For communication base stations, both are important. Frequency stability is directly related to the time synchronization accuracy between base stations, which is the foundation for the normal operation of modes like 5G TDD, and is usually the primary indicator to guarantee. Phase noise mainly affects the purity of the RF transmission signal and the sensitivity of the receiver. When resources are limited, priority should be given to ensuring that frequency stability meets the standard. Why is it necessary to conduct actual tests on OCXO samples instead of just looking at the datasheet? + Datasheets provide typical values, but actual performance can vary depending on production batches and specific usage environments (such as PCB layout, cooling conditions, power supply noise). Actual testing can verify the true performance of samples under specific application conditions, especially short-term frequency drift, phase noise under specific loads, etc. Sample testing is key to reducing risks in the later stages of a project.

READ MORE