Image Sensor Procurement Avoid Pitfalls Guide: 5 Steps for Accurate Pricing, Locking Optimal Inventory Channels

2026-04-14 10:27:12

0

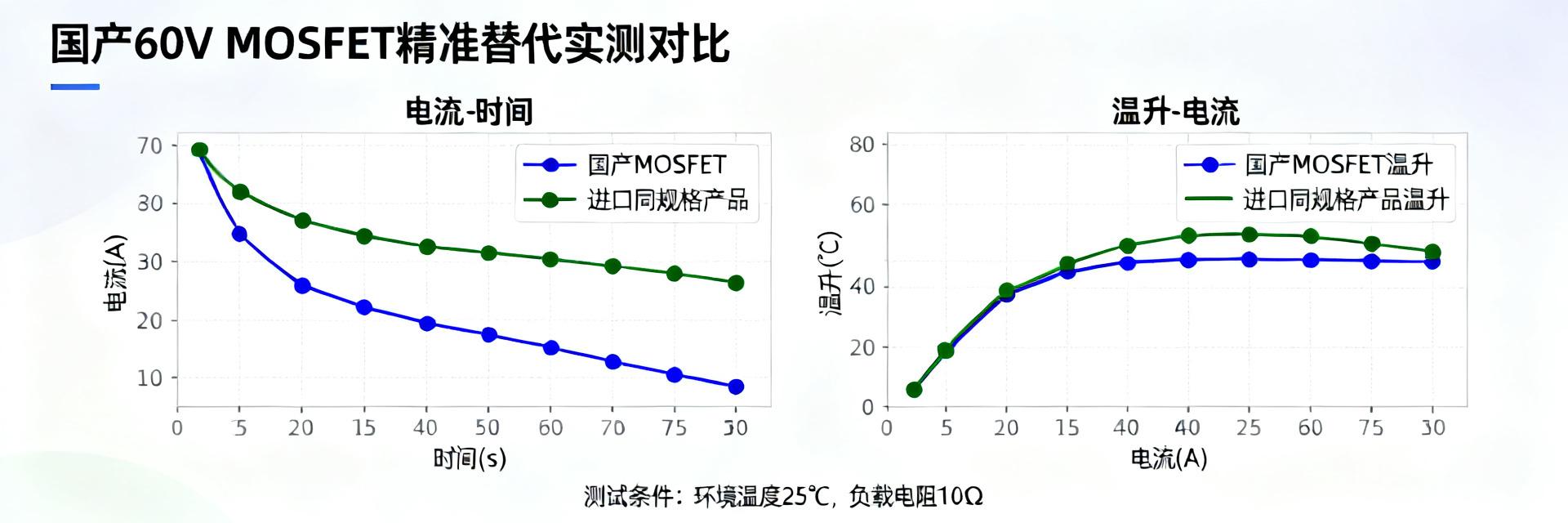

Key Takeaways Precision Matching: Refined selection of resolution and pixel size can reduce redundant hardware costs by approximately 15%-25%. Risk Mitigation: Prioritizing the verification of Authorized Distributor status is key to eliminating refurbished or bulk-new parts. Cost Optimization: Shift from a "unit price perspective" to "Total Cost of Ownership (TCO)," considering payment terms and inventory stability to improve cash flow. Decision Efficiency: Quickly identify the pros and cons of general-purpose models versus customized solutions through comparison tables to shorten the R&D selection cycle. In the development of intelligent vision projects, the selection and procurement of image sensors directly determine the upper limit of product performance and the lower limit of cost. However, faced with a market of complex models, diverse channels, and volatile prices, how to avoid "pitfalls," achieve precise price comparison, and lock in stable and reliable inventory channels is a skill that every hardware engineer and procurement professional must master. This article will break down an effective five-step method for you to help you make optimal decisions in a complex procurement environment. Selection Dimension Blind Procurement (Generic/Price-Oriented) Strategic Procurement (Recommended) Actual User Benefit Resolution/Pixel Size Blind pursuit of high megapixels Customized resolution as needed, larger pixel size 30% reduction in low-light noise, improved night vision clarity Interface Selection Generic Parallel port High-speed MIPI CSI-2 interface 20% reduction in routing area, enhanced system anti-interference performance Channel Strategy Fragmented trade stock Authorized Agency + Long-term scheduling Eliminate stockout/obsolescence risks, ensure material traceability Step 1: Clarify Requirements and Technical Parameters to Establish a Pricing Basis Before starting price comparisons, clearly defining project requirements is the cornerstone for avoiding all subsequent troubles. This requires you to go beyond a simple "need a camera" description and dive into specific performance metrics and system compatibility levels. Core Performance Metrics: Resolution, Frame Rate, and Pixel Size Resolution determines the level of detail, but higher is not always better. For example, when an 8-megapixel sensor is displayed on a 1080p screen, some of its pixel information is redundant. You need to determine the minimum effective resolution based on the end application (e.g., face recognition, QR code scanning). Frame rate concerns motion capture capability; industrial inspection may require over 60fps, while security monitoring might suffice with 30fps. Additionally, pixel size directly affects low-light performance; larger pixels usually mean better light sensitivity, which is crucial for night monitoring applications. Interface and Power Supply: Matching Your System Architecture The image sensor interface (such as MIPI CSI-2, USB, LVDS) must be compatible with the main processor or development board. Choosing the wrong interface means needing extra bridge chips, increasing complexity and cost. Similarly, supply voltage and power consumption must be considered, especially in battery-powered portable devices, where low-power design can significantly extend battery life. Step 2: Multi-channel Information Gathering and Preliminary Screening Once technical parameters are clear, the next step is to broadly collect market information. Information from a single channel often has limitations or price deviations; multi-channel comparison is key to discovering real market prices and quality suppliers. Data Crawling from Mainstream Component E-commerce Platforms Large component e-commerce platforms are excellent starting points for public quotes, inventory data, and datasheets. You can search for target models, such as a high-performance CMOS sensor, across multiple platforms. Focus on recording the unit price, Minimum Order Quantity (MOQ), and spot inventory levels from different suppliers. This data will form the raw database for your price analysis. Identifying Authorized Distributors vs. Factory Channels Not all quotes come from reliable sources. Distinguishing between authorized distributors, independent distributors, and traders is vital. Authorized distributors typically offer original genuine products, full technical support, and stable supply guarantees, even if the price might not be the lowest. You can quickly lock in formal channels by checking the "Authorized Distributor" list on the manufacturer's official website. Meanwhile, for certain domestic sensors, contacting factory sales departments directly may also yield competitive prices and support. L Eng. Lin (Senior Hardware System Architect) 12 years of experience in intelligent vision hardware R&D "In actual procurement, many people overlook the hidden costs of sensor PCB layout. Taking the MIPI interface as an example, if the traces are not strictly length-matched or shielded, the rework cost due to signal integrity issues far exceeds the unit price difference of the sensor." Selection Tip: Pay attention to input voltage margins. Some sensors are extremely sensitive to voltage fluctuations; it is recommended to reserve more than 20% current margin when selecting an LDO. Troubleshooting: If image tearing occurs, first check the PCLK (Pixel Clock) polarity settings and whether decoupling capacitors are placed immediately adjacent to the power pins. Typical Application Scenario Layout Recommendations Low-power IoT Terminal Hand-drawn illustration, not a precise schematic High Frame Rate Industrial Inspection Hand-drawn illustration, not a precise schematic Core Summary Requirements First, Parameters Defined: Precise image sensor procurement starts with clear definitions of core technical parameters such as resolution, frame rate, interface, and power consumption. This is the foundation for all subsequent price comparisons and screening, avoiding cost waste due to specification mismatches. Diverse Channels, Information Wins: Building a comprehensive market view by consulting mainstream e-commerce platforms, identifying authorized distributors, and evaluating factory direct supply channels is the prerequisite for avoiding supply risks and discovering optimal pricing. Total Cost Mindset, Beyond Unit Price: Effective price comparison must comprehensively consider MOQ, lead times, taxes, shipping, and payment terms to calculate the Total Cost of Ownership. The lowest unit price may hide risks of inventory backlog or unstable supply. FAQ Q1: How can I judge if a supplier is reliable in image sensor procurement? Assessing supplier reliability requires a multi-dimensional investigation. First, verify if they are an authorized distributor of the original factory; you can request authorization certificates or check the official manufacturer website. Second, review their years in business, historical cooperation cases, and industry reputation. Third, understand the depth of their spot inventory and standard models, which reflects their supply chain strength. Finally, if possible, conduct small-batch sample procurement first to test product quality, packaging standards, and logistics efficiency as verification before formal cooperation. Q2: Facing multiple quotes, what terms should I focus on negotiating besides price? While price is important, terms that guarantee long-term stable cooperation are more valuable. Negotiation priorities should include: striving for more flexible MOQs to reduce inventory pressure; clarifying and shortening lead times to ensure project progress; discussing competitive tiered volume discounts; negotiating better payment terms to improve cash flow; and clarifying quality guarantees, return policies, and technical support scope. Documenting these terms in writing effectively reduces potential risks in long-term procurement. Q3: What are the procurement strategies for image sensors in small-batch R&D projects? The core challenge of small-batch R&D procurement is MOQ and high unit price. Strategically, first look for authorized distributors or manufacturers that offer sample or small-package services. Second, consider using development boards or evaluation kits, which integrate sensors and basic circuitry to accelerate prototype development. Additionally, pay attention to online platforms focused on serving makers and small-batch customers, as they may stock broken-pack retail inventory. Finally, if project prospects are clear, negotiate a "prototype-to-production" price transition plan with the supplier to pave the way for future expanded procurement. © 2024 Intelligent Vision Procurement Insights | Powering Precise Selection & Efficient Supply Chains

READ MORE

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

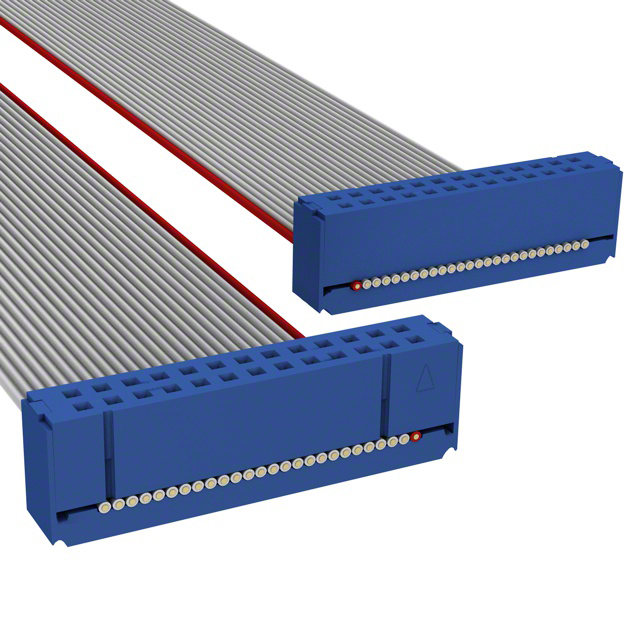

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X S6008LWickmann / LittelfuseSCR 600V 8A TO220

S6008LWickmann / LittelfuseSCR 600V 8A TO220 CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL