新品上市

更多 +

热卖零件

博客

TCS35303-2技术解析:高精度真彩环境光与7kHz闪频检测突破

行业前沿

深度技术专题报告

在智能手机与显示器追求极致视觉体验的今天,自动白平衡(AWB)和屏下环境光感测的精度直接决定了用户的色彩感知。与此同时,源于PWM调光LED和OLED屏幕的频闪,正成为导致用户视觉疲劳的主要元凶。最新的TCS35303-2传感器,正以其独特的高精度真彩能力与业界领先的7kHz频闪检测范围,为这些痛点提供了全新的硬件级解决方案。

作为ams-OSRAM推出的新一代真彩传感器,TCS35303-2并非简单的参数迭代。它通过集成先进的光学滤波器和智能处理单元,将传感器的角色从被动的“感光元件”提升为主动的“环境感知专家”。无论你身处复杂的混合光源环境,还是面对新型显示屏的高频PWM调光,它都能提供超乎想象的精确数据。

真彩传感技术:从“感应亮度”到“媲美人眼”

传统的环境光传感器大多只能测量亮度(Lux),对色温(CCT)的感知非常有限。TCS35303-2通过独特的多通道架构,能够精确捕捉光线的色彩信息,使得设备不再只是知道“有多亮”,更能理解“是什么颜色”,从而真正实现从“感光”到“感色”的跨越。

超越传统XYZ:TCS35303-2的色度通道架构

TCS35303-2的核心优势在于其精心设计的色度通道布局。不同于传统的RGB传感器,它采用了包含多个特殊通道在内的先进架构,能够捕捉到更宽广、更精细的光谱信息。这种设计使其可以精确测量色温(CCT)和照度(Lux),特别是在OLED屏幕下,内置的补偿算法能有效滤除屏幕像素的串扰,提供最真实的环境光读数。

高精度自动白平衡:为摄像头与显示屏设定“黄金标准”

对于智能手机摄像头而言,自动白平衡(AWB)的准确性至关重要。TCS35303-2通过提供高分辨率的色度数据,帮助摄像头在混合光源环境下实现零色偏。同时,在显示屏端,它又能动态管理屏幕色彩,使其完美匹配当前环境光。当你从户外走进室内,屏幕色温会自动调整,整个过程流畅自然。

频闪检测突破:攻克7kHz高频闪技术壁垒

“直接检测” 架构

采用TSF(时间序列滤波器)架构,硬件级捕捉光强瞬时变化,实时输出频率与占空比,准确性远超传统软件算法。

7000Hz 覆盖范围

全面覆盖现有OLED及未来Mini-LED的PWM频率,有效消除摄影摄像中的黑色滚动条(Banding)现象。

实战检验:典型应用场景与系统集成要点

智能手机屏下应用:光路设计与干扰消除

屏下应用是TCS35303-2最具挑战性的场景。为了确保读数真实,需通过特殊导光孔减少屏幕像素串扰。传感器配合动态补偿算法,在显示屏“背后”依然能精准感知外部环境,实现真正的“屏下真彩”。

智能家居与显示终端:从“感光”到“感知”

在汽车座舱或智能电视中,该传感器能高频检测不同角度的频闪,自动调整亮度与色温,实现防眩目与护眼功能。这不仅是亮度调节,更是对复杂光环境的一种“智能感知”。

设计师指南:如何最大化性能潜力

推荐使用标准I2C接口通信,配置关键寄存器以实现最佳性能。

利用内置智能中断功能,设定照度阈值,实现低功耗唤醒。

结合系统级算法,实现长续航智能设备的实时环境感知。

关键摘要:掌控视觉智能的核心

•

高精度真彩传感: 多通道架构实现从感知亮度到感知色彩的进化。

•

7kHz频闪检测: 硬件级TSF架构,完美应对OLED和Mini-LED高频调光。

•

屏下与多场景应用: 优化光路设计与智能算法,提供稳定可靠的环境感知。

常见问题解答

Q: TCS35303-2与普通RGB传感器的主要区别是什么?

A: 普通RGB主要测量RGB三通道强度。TCS35303-2拥有更精细的色度通道,能捕捉丰富的光谱信息,提供远高于普通传感器的色度精度和色温感知。

Q: 7kHz的频闪检测范围对用户意味着什么?

A: 这意味着它可以检测目前主流及未来的PWM调光频率,有效消除拍摄时的banding问题,并辅助屏幕自适应调节,大幅减少用户的视觉疲劳。

Q: 在屏下应用时,如何保证TCS35303-2的精度?

A: 主要通过两方面:硬件光路设计(如导光孔)和算法动态补偿(校准屏幕自发光干扰),确保读数真实可靠。

Q: TCS35303-2是否支持低功耗应用?

A: 支持。其内置智能中断功能,仅在照度或频闪超过设定阈值时唤醒系统,非常适合电池供电设备。

© 2024 高精度真彩传感器技术解析专题 | 极致视觉感知

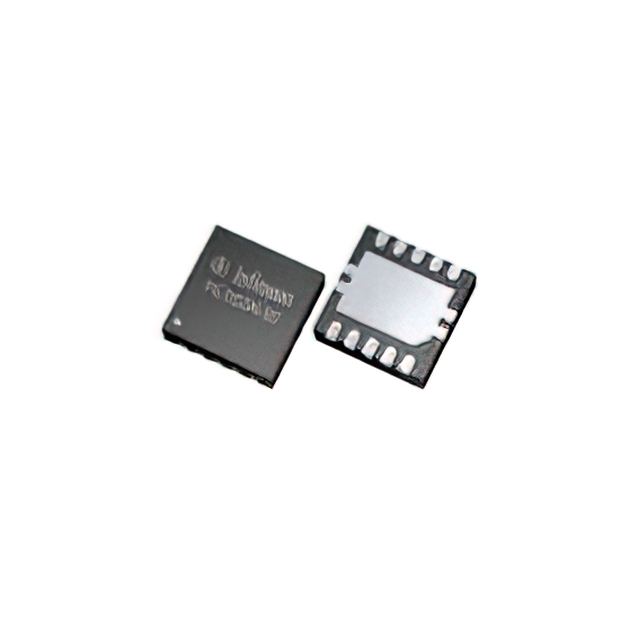

NVMYS4D5N04CTWG 数据手册精讲:40V N沟道 MOSFET 关键参数与特性全解析

深度解析电源设计中的核心器件参数,提升电路可靠性与效率

当电源设计工程师拿起一款40V N沟道MOSFET的数据手册,面对密密麻麻的“VDS”、“RDS(on)”、“Qg”、“Qrr”等参数时,是否感到迷茫?以 NVMYS4D5N04CTWG 为例,这款器件在数据手册中展示了温度对导通电阻的深刻影响,以及开关损耗的量化数据。本文将基于这份数据手册,对40V N沟道MOSFET的关键参数进行逐项解析,帮助工程师在电源、电池管理等应用中精准选型,避免因“读不懂”数据手册而导致的可靠性隐患。

1

一、极限参数与安全边界:低于最高额定值20%的黄金法则

VDS 与 ID:理解“绝对最大值”背后的热限制

先看VDSS,这是漏源击穿电压,定义为当栅源电压VGS=0V时,漏极与源极之间能承受的最大电压。对于NVMYS4D5N04CTWG,其VDSS典型值为40V,这意味着在电路中必须保证漏源电压始终低于这一值,并预留至少20%的降额空间,例如实际工作电压不超过32V。而连续漏极电流ID的额定值则更有讲究:该值实际上受限于封装和结温Tj。数据手册中通常会给出在TC=25℃时的ID最大值,但一旦外壳温度升高,ID的允许值会急剧下降。工程师在设计散热系统时,必须参考TC对ID的影响曲线,而不是盲目相信标称电流值。实际应用中,长期工作的热点温度应控制在120℃以下,才能保证器件的长期可靠性。

脉冲电流 (IDM) 与雪崩能力 (EAS):应对瞬态浪涌的底气

在电机驱动或感性负载启动的瞬间,MOSFET会承受远高于稳态电流的浪涌。脉冲漏极电流IDM反映了器件在短时脉冲下的承受能力,这得益于硅芯片的热容缓冲。而单次雪崩能量EAS是衡量器件鲁棒性的关键指标,它表明在关断感性负载时,器件能够吸收多少能量而不会发生雪崩击穿。数据手册中的“单脉冲雪崩能量”图展示了EAS与起始结温的关系,随着结温升高,EAS能力会显著下降。工程师在系统设计中,应确保实际产生的雪崩能量远低于手册中的额定值,并考虑在最恶劣温度下仍有余量。通过查阅这张曲线图,可以定量评估系统的可靠性,避免在电机堵转等极端工况下发生损坏。

2

二、导通特性深度解析:RDS(on) 的温度系数与栅极驱动

关键导通参数

测试条件 (Typical)

典型值

RDS(on)

VGS=10V, Tj=25℃

4.5 mΩ

RDS(on) 高温

VGS=10V, Tj=125℃

约 1.5~2x 倍

VGS(th)

ID=250µA

2V ~ 4V

RDS(on) 不仅仅是“毫欧”:温度与栅极电压的联动效应

NVMYS4D5N04CTWG的导通电阻RDS(on)是计算导通损耗的核心参数。数据手册会给出在VGS=10V、ID=50A、Tj=25℃时的典型值,例如4.5mΩ。但必须注意,RDS(on)具有显著的正温度系数,即随着结温Tj升高,电阻值会增大。在Tj=125℃时,RDS(on)可能变为25℃时的1.5到2倍。同时,栅源电压VGS对RDS(on)的影响同样关键:当VGS从10V降至5V时,RDS(on)会急剧增大,因为MOSFET未进入深度饱和区。因此,为了使导通损耗最小化,栅极驱动电压应足够高(推荐10V),尤其是在大电流应用中。忽略温度系数和驱动电压,将导致实际损耗远高于理论计算,造成散热系统过热。

跨导 (gfs) 与转移特性:栅极电压如何控制大电流

跨导gfs和转移特性曲线(ID vs VGS)揭示了栅极电压对漏极电流的控制能力。通过该曲线,工程师可以确定器件的开启阈值电压VGS(th)以及跨导的线性区。例如,NVMYS4D5N04CTWG的典型VGS(th)可能在2V到4V之间。当VGS高于阈值时,ID开始随VGS线性增加,斜率即为跨导。高跨导意味着较小的栅压变化就能产生较大的电流变化,有利于提高系统的响应速度。但在3.3V或5V逻辑电平驱动场景下,如果VGS较低(例如4.5V),器件可能只工作在线性区,导致RDS(on)远高于数据手册标称值。因此,理解转移特性曲线对判断器件在低压驱动下的适用性至关重要。

3

三、动态特性与开关损耗:米勒平台与栅极电荷的“密码”

栅极电荷 (Qg) 与米勒电容 (Crss):决定开关速度的关键

开关损耗是高频应用中的主要损耗来源,而栅极电荷Qg、栅漏电荷Qgd(米勒电荷)和输入电容Ciss是解读开关行为的关键。数据手册中的栅极电荷波形图展示了充电过程:从VGS上升至阈值开始,到米勒平台结束。米勒平台的出现是因为VDS开始下降,Crss反馈导致VGS暂时稳定。Qg的总量决定了驱动器的驱动能力需求,而Qgd决定了米勒平台的宽度。对于NVMYS4D5N04CTWG这类低压MOSFET,较低的Qg和Qgd是实现高频开关、降低开关损耗的核心。工程师可以通过Qg值估算驱动电路的平均功耗(Pgate = Qg × Vgs × fsw),并据此选择驱动芯片的峰值电流。

开关时间与二极管反向恢复 (Qrr):交越损耗与 EMI 权衡

开关时间参数(ton、toff、tr、tf)以及体二极管的反向恢复电荷Qrr直接影响开关轨迹和EMI特性。较短的开关时间可以降低开关损耗,但过快的di/dt和dv/dt会加剧电压尖峰和电磁干扰。数据手册中的典型开关特性曲线展示了不同栅极电阻下的开关波形,工程师可以通过调整栅极电阻来平衡效率与EMI。体二极管的Qrr在桥式电路中尤为重要:在同步BUCK变换器中,上管关断后下管体二极管续流,当下管再次开通时,其反向恢复电流会增加上管的导通损耗和电压应力。因此,在硬开关应用中,选择低Qrr的MOSFET有助于提升整机效率。

4

四、数据手册“读图”实战:从特性曲线到应用验证

输出特性与传导损耗:如何根据曲线估算导通电阻

数据手册中的“典型输出特性”曲线(ID vs VDS)是验证器件性能的直观工具。在特定VGS和ID下,曲线上的点对应着VDS压降。通过公式 RDS(on) = VDS / ID,可以反算出器件在该工作点的实际导通电阻。例如,在VGS=10V、ID=50A时,若VDS为0.225V,则RDS(on)约为4.5mΩ。通过在不同温度下(如25℃和125℃)读取多组数据,可以验证数据手册表格参数的温度系数。这种“读图”方法能帮助工程师在早期设计阶段,就对导通损耗有更准确的认识,避免因参数值漂移而导致的系统失效。

安全工作区 (SOA):单脉冲与重复脉冲的生存指南

正向偏置安全工作区(FBSOA)曲线是判断MOSFET在瞬态工况下是否会被烧毁的唯一标准。SOA图通常由四条边界线围成:RDS(on)限制(大电流、小电压)、电流限制(最大IDM)、功率限制(恒定功耗,对应一定的脉冲宽度)和击穿电压限制(最大VDS)。在开关电源启动、短路或负载突变时,器件可能瞬间工作在大电流、高电压的线性区。此时,工程师必须确保该工作点落在SOA曲线之内,并考虑脉冲宽度和占空比的影响。重复脉冲工况下,器件的结温会逐渐累积,需要参考更复杂的热模型,但SOA曲线是进行快速评估的最直接依据。

关键摘要

降额设计与热管理: NVMYS4D5N04CTWG的极限参数VDSS和ID受结温Tj严格限制,实际设计需降额20%以上,并依据TC-ID曲线进行散热系统设计,将Tj控制在120℃以下。

RDS(on)的温度与电压敏感性: 导通电阻RDS(on)具有正温度系数,且在低VGS时急剧增大。为实现低导通损耗,推荐采用10V栅极驱动,并考虑高温下电阻值上升带来的损耗变化。

开关损耗由Qg与Qrr主导: 高频应用中,需关注总栅极电荷Qg和米勒电荷Qgd以估算驱动功耗和开关速度,同时注意体二极管反向恢复电荷Qrr对桥式电路效率的影响。

SOA是判断鲁棒性的工具: 在瞬态或短路工况下,需确保工作点落在FBSOA曲线内,尤其是功率限制和击穿电压限制边界,以保障器件不会因过应力而损坏。

常见问题解答

Q: NVMYS4D5N04CTWG的VGS驱动电压选择有什么讲究?

该器件的RDS(on)在VGS=10V时达到最佳性能。若使用5V或3.3V驱动,其导通电阻会显著增大,导致导通损耗剧增。驱动电压过低时器件可能无法完全饱和,进入线性区工作,尤其在重载下非常危险。因此,建议采用10V的专用栅极驱动电路。

Q: 如何利用数据手册估算MOSFET的开关损耗?

首先从手册中找到栅极电荷Qg和开关时间(ton,toff)。开关损耗主要由米勒平台期间的电压电流交越产生,精确计算需结合Qg波形图。常用估算公式为 Psw = 0.5 × VDS × ID × (tr+tf) × fsw。对于NVMYS4D5N04CTWG,其Qg值较低,适合高频应用。

Q: 体二极管的反向恢复特性对电路有什么影响?

体二极管的反向恢复电荷Qrr会导致额外的开关损耗和电压尖峰。在同步整流等桥式拓扑中,下管体二极管的反向恢复电流会流经上管,增加上管的导通损耗和应力。低Qrr的MOSFET有助于降低这部分损耗并改善EMI。

Q: 安全工作区(SOA)曲线在实际设计中有多重要?

SOA曲线是判断器件能否承受启动、短路等瞬态大电流的权威依据。工程师需确保在特定脉冲宽度和占空比下,电路中的电压电流组合始终落在SOA边界之内。忽略SOA可能导致MOSFET在毫秒级内因热失效而烧毁。

Q: RDS(on)的温度系数为什么会影响系统的长期可靠性?

RDS(on)的正温度系数意味着随着结温升高,导通电阻增大,从而产生更多热量,形成正反馈。如果散热设计不足,可能引发热失控。因此,高温下的RDS(on)值决定了散热器的设计要求,是保证系统在恶劣环境下稳定运行的关键。

本文由资深电源工程师精讲 | 关键词:MOSFET, NVMYS4D5N04CTWG, 数据手册, 电源设计, RDS(on), SOA