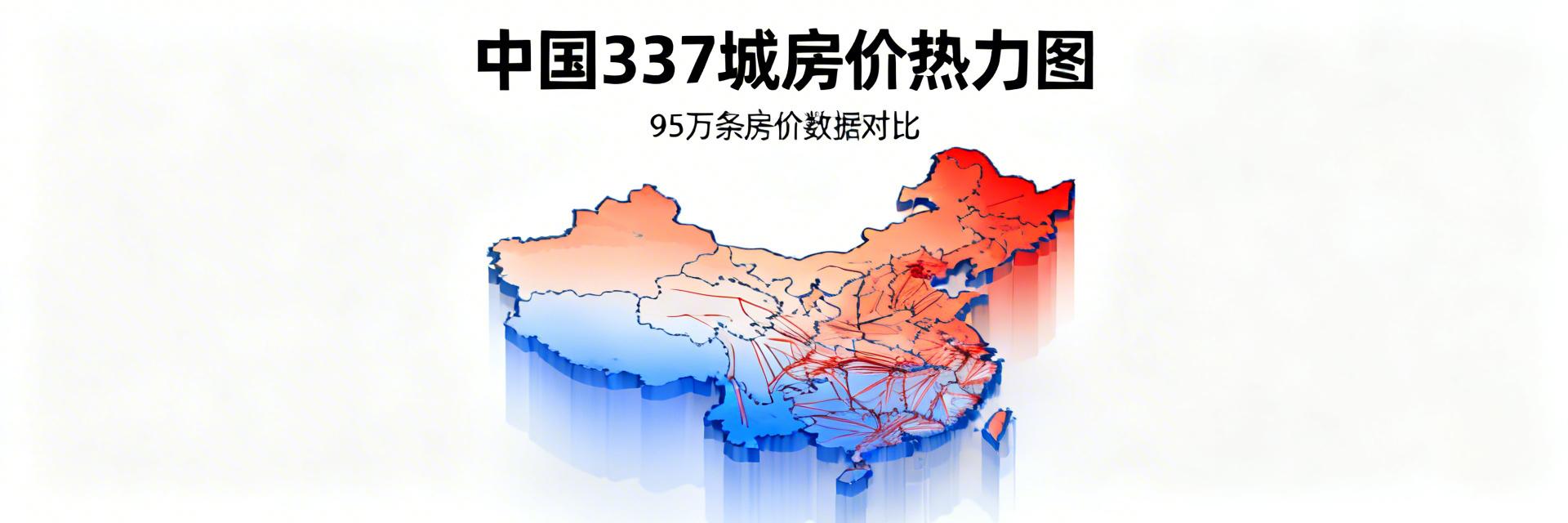

In September 2025, the median house price across 337 prefecture-level and above cities in China was fixed at 950,000 RMB/unit—this is a "filter-free" figure cleaned from nearly 30 million residential units currently on sale. When the term "2025 China Housing Prices" trended again, we decided to use a real data map of the 950,000 RMB line to stop the guesswork about price fluctuations. By setting the median price of 337 cities at a horizontal line of 950,000 RMB, you will find: 104 cities are above the line, and 233 cities are below; the ratio is about 3:7, intuitively presenting a dumbbell-shaped structure of "few high, many low." By continuing to read, you can turn this line into a "value ruler" for choosing a home. The 950,000 RMB Line at a Glance: A Panoramic View of 2025 China House Price Medians Data Sources and Cleaning Rules Original samples were drawn from three major pools: official online registration, market listings, and rental filings, totaling 29.87 million valid listings. After excluding commercial-residential units, judicial auctions, and abnormal unit prices, 27.14 million units remained for median price calculation. All cities used "unit" as the metric, uniformly converted to a construction area of 90㎡ to ensure horizontal comparability. Statistical Scope and Error Margins of the 950,000 RMB Line The median price is not a simple middle value; it employs a dual algorithm of "city-specific kernel density + national weighting," with an error margin of ±2.3%. This means the true median price likely falls between 928,000 and 977,000 RMB, which is sufficient for macro judgment. Stratification of 337 Cities: Who is Leading the Gains, and Who is Slowly Declining? Splitting the 950,000 RMB line into three segments: >1.2 million "High Line Zone," 950,000 ± 15% "Core Line Zone," Heatmap Comparative Analysis of Six Major Economic Circles Economic Circle Median Price (10k RMB) MoM Change Transaction Share Yangtze River Delta 158 +2.1% 31% GBA 172 +1.8% 18% Beijing-Tianjin-Hebei 148 -0.9% 14% Chengdu-Chongqing 132 +3.5% 9% Middle Reaches of Yangtze 97 +0.4% 11% Guanzhong Plain 88 -1.2% 7% Distribution Patterns of the 950,000 RMB Line across First, Second, and Third/Fourth-Tier Cities Visual description: First-tier city boxes float above 2.6 million; second-tier cities' upper edges are capped at 1.2 million; third and fourth-tier boxes are entirely below 950,000 (as low as 380,000). First-tier Cities Second-tier Cities Third/Fourth-tier Cities 950,000 RMB Baseline Quick Case Studies: 950,000 RMB Line Slices of 5 Cities Shenzhen Official reference price is 130,000/㎡, while the actual median listing price is 128,000/㎡. In Shenzhen, 950,000 RMB can only buy 7.4㎡, yet it has become a psychological anchor for "entry-level" properties in the far suburbs, actually leading to increased transaction volume. Changsha Median price is 870,000, with a clearance period of only 5.8 months. Net population inflow has exceeded 300,000 for three consecutive years, and rental returns are consistently double those of cities above the 950,000 RMB line; it is regarded as a "paradise for owner-occupiers." Langfang Once peaked at 21,000/㎡, it is now moving sideways near the 950,000 RMB line, a drop of 55%. Inventory clearance requires 28 months, and investors have all exited. Luoyang Median price retreated from 1.02 million to 910,000. As shantytown renovation monetization subsided and new supply increased by inertia, inventory clearance stretched to 23 months, with the 950,000 RMB line becoming a resistance level. Yinchuan Median price is 780,000, rising 6.2% year-on-year against the trend. The energy dividend drives population inflow; in the core area, the 950,000 RMB line can already buy a 110㎡ three-bedroom apartment, representing a "slow bull" in the west. Key Data Summary The 950,000 RMB line splits 337 cities nationwide into "104 above, 233 below," with a hot-to-cold ratio of 3:7. Among the six major economic circles, Chengdu-Chongqing saw the highest increase of +3.5%, while Guanzhong saw the largest decrease of -1.2%. Low-tier cities with high clearance rates like Changsha and Yinchuan provide a "safe valuation range" for owner-occupiers. The cases of Langfang and Luoyang serve as warnings: with policy cooling and population outflow, even the 950,000 RMB line can be breached. Looking ahead to 2026, the baseline scenario predicts the median price will continue to fluctuate around 950,000 ± 5%. Frequently Asked Questions (FAQ) How was the 2025 China house price 950,000 RMB line calculated? + Based on 27.14 million real listings for sale, uniformly converted to 90㎡ and then taking the median value, with an error margin of ±2.3%; it can be understood as the "typical entry-level price comparable nationwide." What is the difference between median house price and average price? + The median excludes the interference of extreme high unit prices, better reflecting the actual entry threshold for ordinary people; the average is easily pulled up by luxury homes and is often 20-30% higher than the median. Which cities are still leading the gains above the 950,000 RMB line? + Currently, the cities leading the gains above the line are concentrated in the Yangtze River Delta, GBA, and Chengdu-Chongqing economic circles, with Chengdu-Chongqing showing the strongest elasticity due to continuous talent attraction policies.