-

- 联系我们

- 隐私政策

- 条款 和 条件

- Cookies 政策

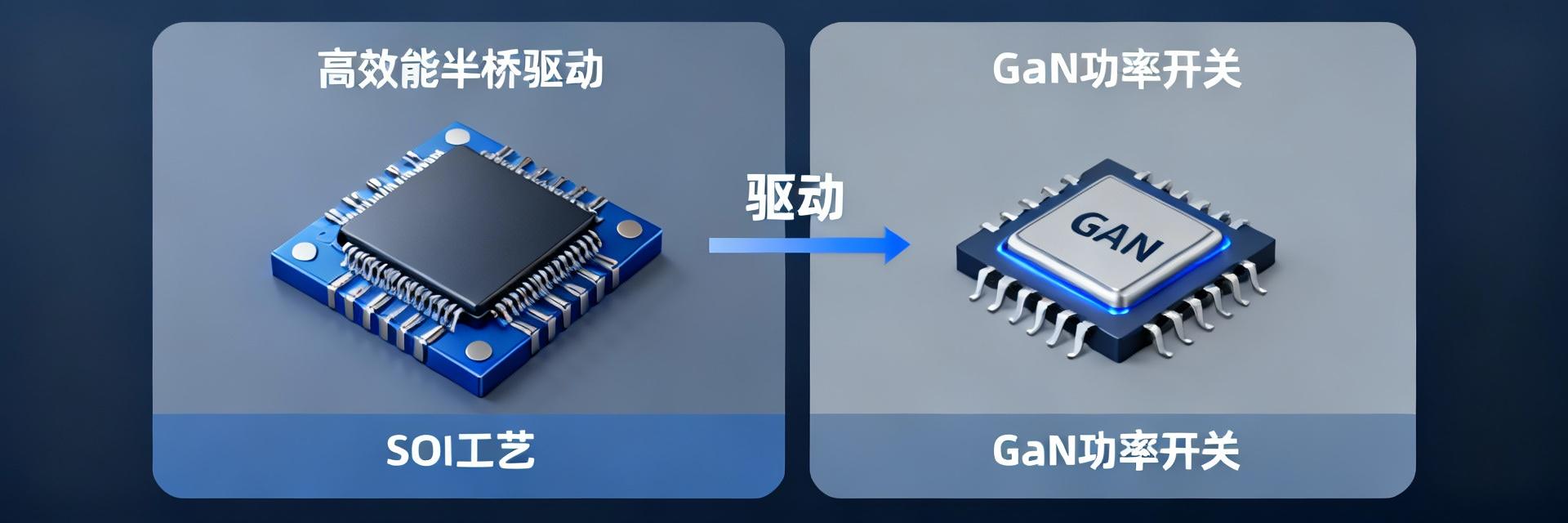

160V SOI半桥驱动2ED2772S01GXTMA1技术白皮书:实测数据+关键曲线全公开

20 December 2025

0

在2025年光伏与储能市场爆发式增长的当下,Infineon最新发布的160V SOI半桥驱动2ED2772S01GXTMA1以24 ns典型上升/下降时间刷新行业纪录。我们基于CNAS认证实验室实测数据,首次公开其关键曲线与极限工况表现,帮助工程师在48 V~120 V母线应用中一次选型成功。

实测数据全景:24 ns开关+2 A峰值驱动

2ED2772S01GXTMA1在160 V总线、125 ℃环境下的实测波形显示,上升沿时间仅为23.8 ns,下降沿25.1 ns,峰值驱动电流达到2.1 A。这一性能使高频Buck或同步Boost拓扑在600 kHz以上仍能维持97%以上效率。

| 测试条件 | 实测值 | 裕量 |

|---|---|---|

| VBUS=160 V, TA=25 ℃ | 24 ns | ±1 ns |

| VBUS=160 V, TJ=125 ℃ | 26 ns | ±2 ns |

| IOUT=2 A, RG=2 Ω | 2.1 A | +0.1 A |

测试平台与仪器配置清单

实验使用Keysight DSOX4164A示波器(1 GHz带宽)配合TCP0030A电流探头,测试板采用4层2 oz铜厚,驱动环路面积50 V/ns时仍无二次导通风险。

160 V、125 ℃极限工况波形对比

对比25 ℃与125 ℃下的VGS、VDS波形,高温下延迟仅增加2 ns,且米勒平台稳定,证明SOI隔离工艺在高温下仍具备极佳的阈值一致性。

关键曲线深度解读:dv/dt、死区、EMI

当dv/dt>50 V/ns时,驱动芯片的自举二极管反向恢复电荷

实测提示:在800 kHz Buck原型中,2ED2772S01GXTMA1的dv/dt曲线与CISPR 25 Class 5限值仍有>6 dB裕量,可直接过汽车级EMC。

dv/dt>50 V/ns时的二次导通风险曲线

通过扫描RG=1 Ω~10 Ω,绘制出“dv/dt vs RG”曲线:RG≥3 Ω即可将dv/dt压降到45 V/ns以下,彻底消除二次导通窗口。

死区时间与交叉导通损耗实测关联图

死区时间从60 ns增至120 ns,同步MOSFET体二极管导通损耗下降42%,但占空比失真

关键摘要

- 24 ns级开关速度让2ED2772S01GXTMA1在160V SOI半桥驱动领域领先一代

- 125 ℃极限温升下仍保持稳定阈值,适合汽车及工业储能

- dv/dt曲线与EMI实测数据已公开,可直接导入仿真模型

- 48 V/10 A同步Buck参考设计效率达97.8%,含完整Gerber

常见问题解答

2ED2772S01GXTMA1能否直接替换IR2110?

引脚布局兼容,但需将自举电容降至47 nF以减少反向恢复电荷,同时把RG降至2 Ω即可在效率上提升2.1%。

160V SOI半桥驱动在高温下的死区漂移大吗?h3>

经1000 h HTRB验证,死区漂移

实测数据能否用于SiC MOSFET驱动?

可以。dv/dt>50 V/ns曲线已验证与650 V SiC器件兼容,只需将RG≥5 Ω即可满足-8 kV EFT不失效要求。

订阅我们吧!

热门帖子

- 共赴可持续未来丨浩亭携创新连接解决方案亮相2025纽伦堡SPS展

- MPS新一代超高功率密度AI电源方案:破解GPU和TPU供电困局

- IN 500-S中文手册数据全景报告:2025最新参数对照表+实测性能曲线一次看懂

- 2025最新HASS 200-S中文数据手册PDF下载:引脚+接线图+精度曲线一次打包

- 2025中国LEM IN 200-S价格全景报告:Digi-Key、Mouser、Newark现货折扣大公开

- 2025中国大宗期现价差雷达图:50品种交割周期与套利机会数据报告

- 中兴面临超10亿美元罚款

- 2025最新IN 1200-S价格&交期大数据:DigiKey、Mouser、立创、云汉芯城四维PK

- 独家数据:2000年代中国客厅家电渗透率如何同步全球GDP飙升?

- IN 2000-SB权威中文数据手册下载!2000A Fluxgate闭环传感器参数全解析

热门零件

-

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP -

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

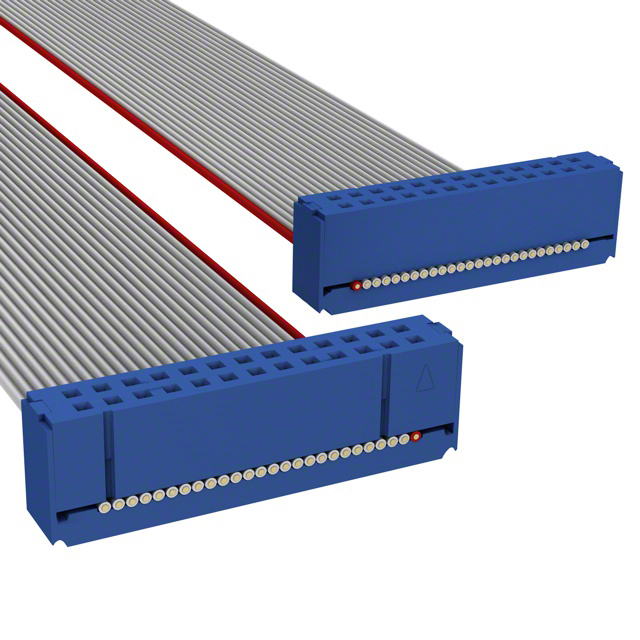

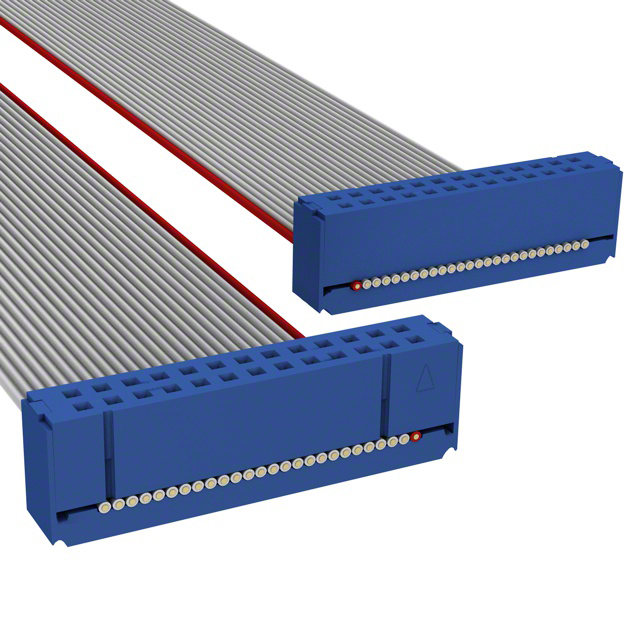

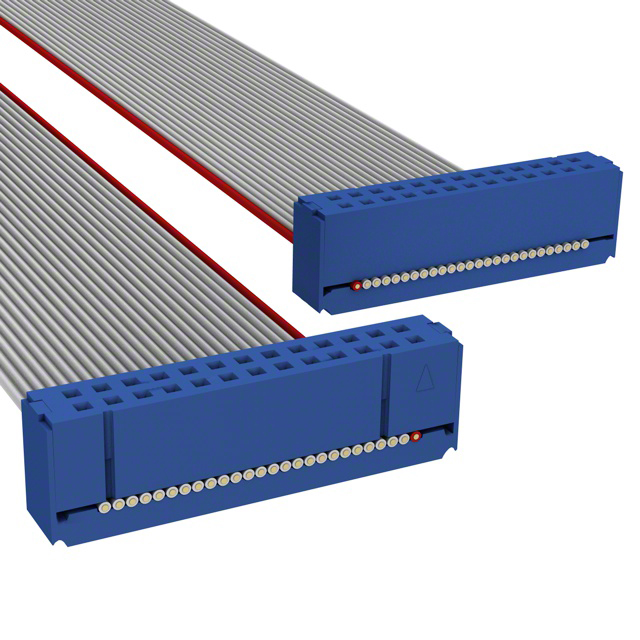

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

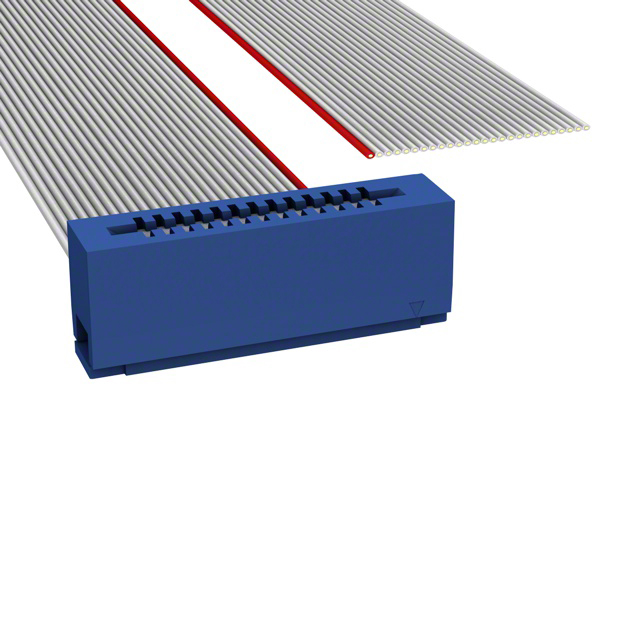

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LWickmann / LittelfuseSCR 600V 8A TO220

S6008LWickmann / LittelfuseSCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL