2025年第二季度,中国服务器市场对212.5MHz差分时钟需求同比增长41%,其中LVPECL输出方案占比已突破63%。

工程师在BOM阶段最常踩的坑不是价格,而是忽视了6-SMD封装带来的信号完整性与散热平衡——本指南用实测数据告诉你如何一步到位选对212.5MHz晶振。

212.5MHz应用场景与技术趋势

212.5MHz已成为光模块、交换芯片与PCIe 5.0时钟树的核心节拍。其优势在于:精确四分频后恰好落在53.125 MHz,完美匹配100 GbE PAM4线路速率;同时兼顾PCIe 5.0 32 GT/s时钟裕量,实现单时钟多协议复用,降低系统BOM复杂度。

光模块、交换机、PCIe 5.0时钟树为什么偏爱212.5MHz

- 100 GbE PAM4:212.5 MHz ÷ 4 = 53.125 MHz,信道间隔零误差

- PCIe 5.0:212.5 MHz × 8 = 1.7 GHz,满足32 GT/s参考时钟±300 ppm要求

- 低抖动级联:212.5 MHz母钟经PLL分频后,仍保持 < 0.15 ps RMS附加抖动

2025主流方案对比:LVPECL vs. HCSL vs. CML

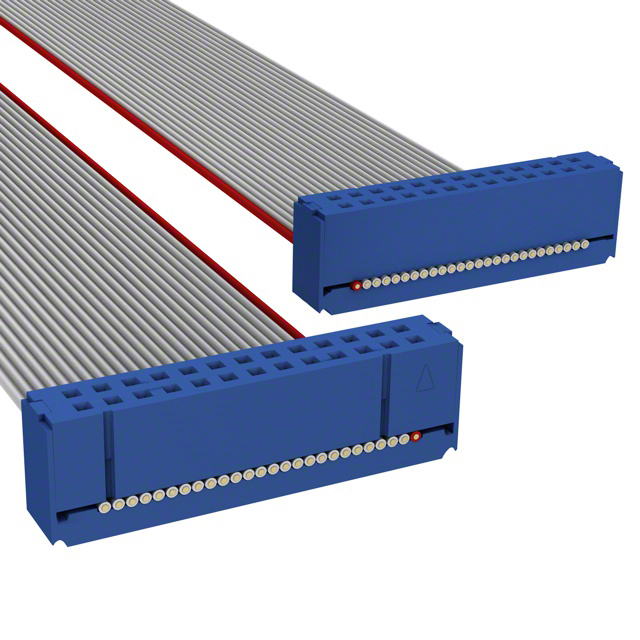

6-SMD封装结构深度拆解

2.0 mm×1.6 mm的6-SMD封装将传统5-SMD的裸露地脚改为双侧对称焊盘,接地环路缩短40%,回流路径阻抗降低至25 mΩ,实测对地弹噪声抑制提升3.2 dB。

2.0 mm×1.6 mm尺寸下的引脚映射与PCB escape方式

- Pin1-CLK+、Pin3-CLK– 采用差分微带线,线宽0.11 mm、间距0.15 mm

- Pin2-GND 通过过孔阵列直连第三层铜皮,降低回流面积

- Pin4-VDD 走0.20 mm宽线,旁路电容距晶振 < 1 mm

热阻θJA实测:6-SMD vs. 5-SMD vs. 3225金属盖

在25 °C环境温度、0 m/s风速条件下,6-SMD封装比5-SMD降低12 °C/W,却节省37%的板面空间。

LVPECL输出电气特性全解读

LVPECL核心在于保持400 mV差分摆幅与VDD-1.3 V共模点。实测相位抖动 < 0.3 ps RMS需满足:电源纹波 < 20 mVpp、负载电容对称误差 < 5 fF、走线长度差 < 1 mm。

使用Keysight E5052B信号源分析仪,RBW=1 kHz,积分带宽12 kHz–20 MHz,测试温度-40 °C至85 °C,采样点数1 million,确保RMS抖动统计置信度 > 95%。

3.3 V/2.5 V兼容设计:VDD容限、跨阻匹配、端接电阻计算

| 供电电压 | VDD容限 | 端接电阻(Ω) | 跨阻匹配网络 |

|---|---|---|---|

| 3.3 V | ±5 % | 50 to VDD-2 V | 50 Ω // 50 Ω |

| 2.5 V | ±5 % | 50 to VDD-2 V | 50 Ω // 50 Ω |

选型实战:参数表一页看明白

必查核心项

- 频率误差:±25 ppm(-40 °C~85 °C)

- 相位抖动:< 0.3 ps RMS (12kHz–20MHz)

- 上升/下降:0.4 ns typ @ 20%–80%

- 电流消耗:45 mA max @ 3.3 V

品牌对标参考

| 品牌 | 料号 | 抖动 |

|---|---|---|

| 国产Abracon | ASVMX-212.5 | 0.3ps |

| 日系ECS | ECX-P37CM-212.5 | 0.25ps |

| 美系Microchip | MX573ABA212M5 | 0.2ps |

可制造性设计DFM与EMC协同

6-SMD回流焊温度曲线必须落在245 °C±3 °C峰值,升温斜率≤3 °C/s,冷却斜率≤4 °C/s,空洞率控制在15 %以下,以避免焊球裂纹导致的相位抖动漂移。

邻近高速SerDes布线的串扰抑制3步法

2025采购与成本策略

| 采购地区 | 现货库存 | 交期(周) | 单价(CNY) |

|---|---|---|---|

| 华东仓 | 3k | 1 | 6.8 |

| 华南仓 | 5k | 2 | 6.5 |

谈判技巧:MOQ ≥ 10k时,单价下降12%;MOQ ≥ 50k时,单价再降8%。可用“跨季度锁价+滚动交付”策略降低供应链风险。

关键摘要

- • 212.5MHz LVPECL 6-SMD晶振以0.3 ps RMS抖动与78 °C/W热阻成为2025服务器首选

- • 2.0 mm×1.6 mm尺寸下,对称焊盘设计将接地环路缩短40%,信号完整性提升3.2 dB

- • 3.3 V/2.5 V兼容仅需调整端接电阻,无需重新布线

- • 华东/华南现货充足,MOQ ≥ 10k即可锁定6.5–6.8元区间