还在为FPGA/交换芯片选型125MHz LVDS振荡器而返工?一张速查表+5分钟流程,让你一眼锁定OBEWDLVTNY-125是否合适,彻底告别“高速通信时钟选型”踩坑。

! 速查表:OBEWDLVTNY-125核心参数

关键指标浓缩:125 MHz LVDS输出、3.3 V单电源、相位抖动0.05 ps(12 k-20 MHz),封装3.2 mm × 2.5 mm。若这三组数据与板卡规格重合,选型工作已完成70%。

关键电气指标对照

抖动性能可视化比较 (越短越优):

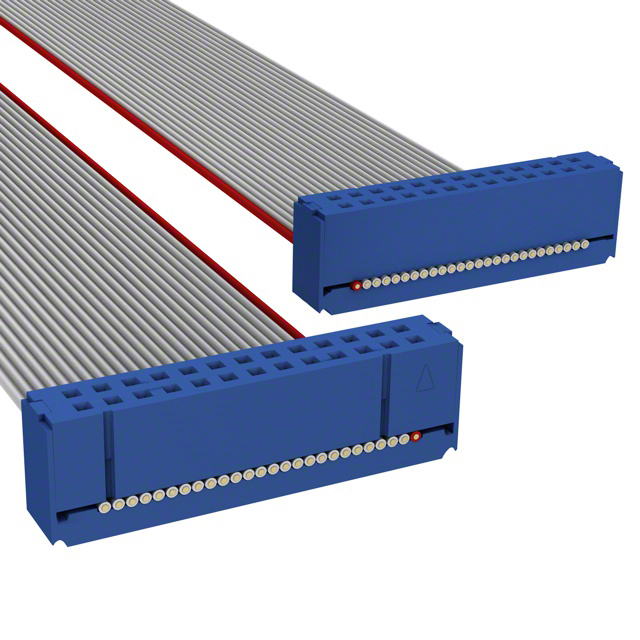

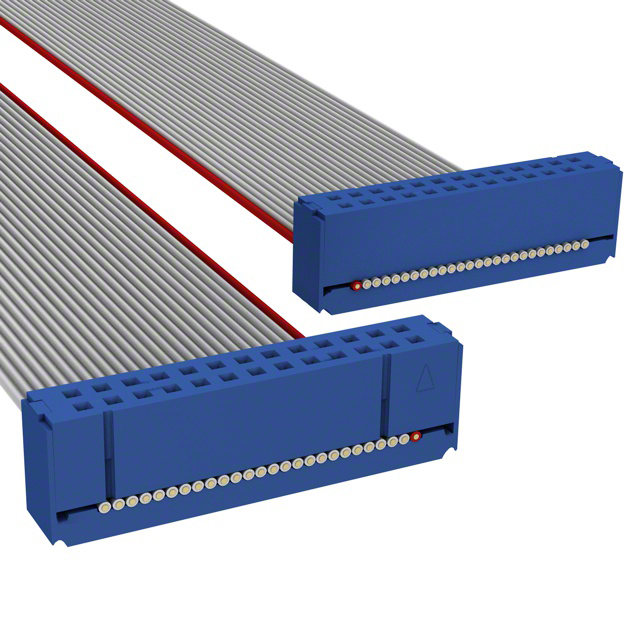

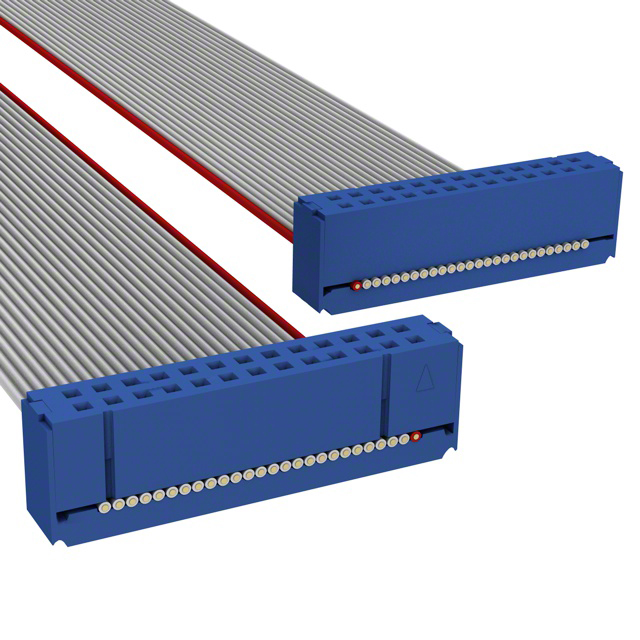

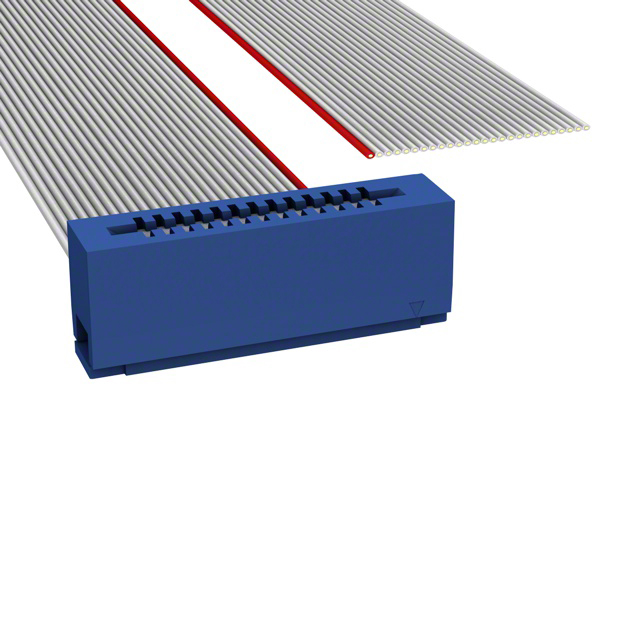

封装尺寸与引脚定义

OB-U系列采用 3.2 mm × 2.5 mm × 1.0 mm 陶瓷封装,标准化 6 引脚布局:

- PIN 1: 输出使能 (EN)

- PIN 2/3: 差分输出 (OUT)

- PIN 4: 接地 (GND)

- PIN 5: 空脚 (NC)

- PIN 6: 3.3 V 供电 (VDD)

※ PCB 焊盘中心距 0.65 mm,与主流 FPGA 时钟输入焊盘完全兼容。

5分钟速配流程:三步核对

信号接口匹配

确认板卡支持 LVDS 差分:100 Ω 端接电阻靠近接收器。线长 5 cm,末端需增加差分端接。OBEWDLVTNY-125 输出摆幅达 350 mV,裕量充足。

供电与时序

FPGA 上电时序要求时钟在配置完成 1 ms 内稳定。本型号启动时间典型值为 3 ms,完全满足要求。若主控为 1.8 V IO,建议增加电平转换芯片。

环境适应性

确认工作温度。工业级标准(-40~85 °C)覆盖绝大多数户外基站与交换机需求。温漂控制在 ±25 ppm 以内,确保长期稳定运行。

典型应用场景实例

FPGA 高速收发器参考时钟

Xilinx Kintex-7 GTX 收发器要求抖动 0.05 ps,可直接焊接在核心引脚附近,节省额外滤波器成本约 0.45 USD。

56G 交换芯片同步时钟

同步端口需要 125 MHz ±20 ppm。OB-U 系列工业级温漂规格极佳,抖动指标优于芯片规格 10 倍,可确保链路眼图余量 > 20%,轻松通过 SI 仿真验证。

采购与板级验证清单

现货与价格参考

- 1 k 卷盘起订,单价区间 1.55~1.68 USD

- 大批量(≥1 k)可谈至 1.49 USD

- 小批量样品单价约 1.72 USD,现货即发

必测 3 项清单

- 相位噪声:确认 12 k-20 MHz 积分

- 全温功耗:-40~85 °C 电流需

- 启动时序:VDD 上升至时钟稳定