应用场景驱动:为何312.5MHz LVDS成为高端标配?

312.5MHz频率并非凭空而来,它是高速串行器/解串器(SerDes)链路中常见的参考时钟频率,尤其在数据速率达到25Gbps或更高的应用中。这一频率为PCIe、以太网和光纤通道等协议提供了精确的时钟基础,确保了高速数据流的可靠同步与恢复。

AI加速卡与GPU集群

在AI训练和推理集群中,多张GPU或加速卡需要协同工作。它们之间的高速互连(如NVLink)对时钟同步的精度要求极高。312.5MHz LVDS晶振为这些互连提供低抖动、高稳定的参考时钟,确保数据在GPU间高速传输时保持极低的误码率。

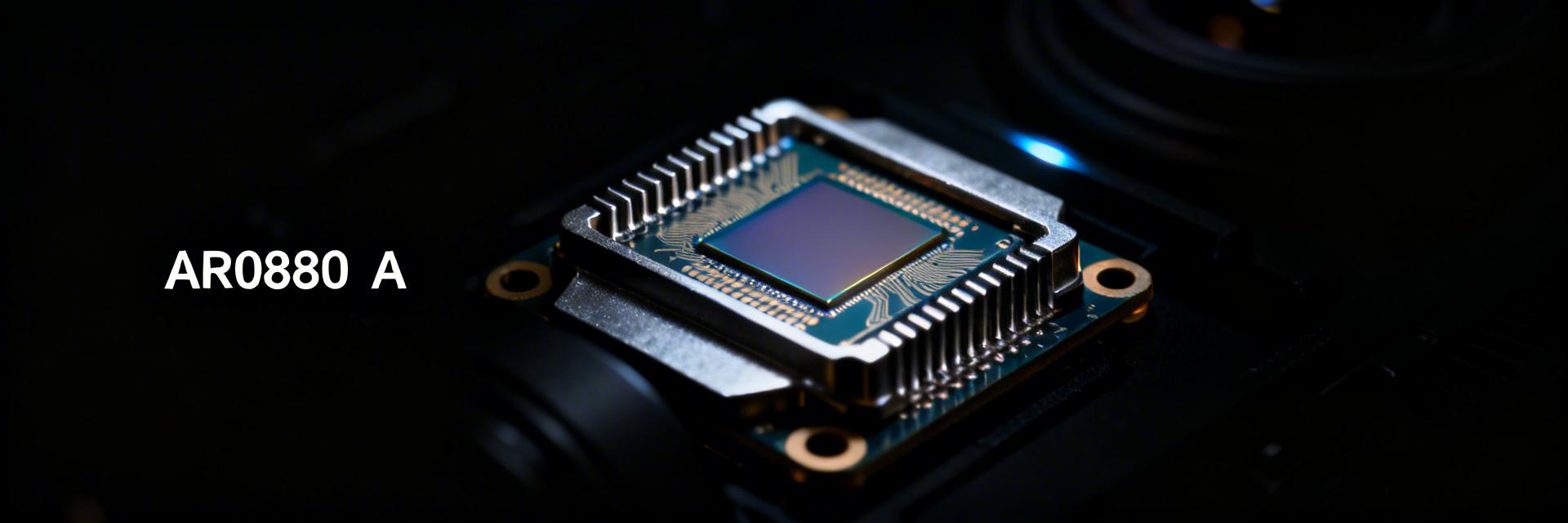

高速光通信模块 (400G/800G)

400G及更高速率的光模块内部,光电转换和信号处理电路需要在极高频下精确同步。312.5MHz LVDS晶振产生的低相位噪声时钟,是驱动高速调制器、跨阻放大器和时钟数据恢复(CDR)电路的核心。

频率精度与稳定性:系统同步的基石

频率精度定义了晶振输出频率与标称值(312.5MHz)的初始偏差,而稳定性则描述了该频率在各种环境条件下(主要是温度变化)保持恒定的能力。这两者是确保整个数字系统时序一致性的根本。

相位噪声与抖动:信号纯净度

对于312.5MHz LVDS晶振,在12kHz至20MHz积分带宽下,RMS抖动通常要求低于100飞秒(fs)。

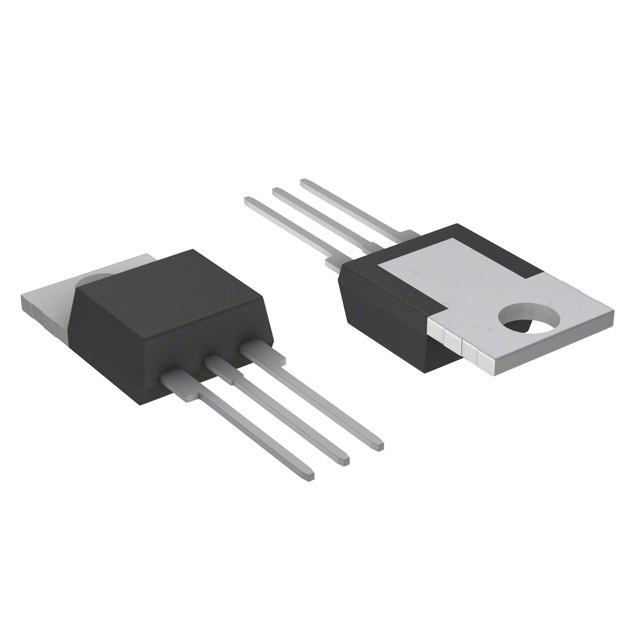

输出逻辑对比

电源与功耗:高密度设计的约束

312.5MHz LVDS晶振常见工作电压为3.3V。PSRR(电源噪声抑制比)至关重要,高PSRR值意味着晶振在嘈杂的电源环境下仍能输出纯净时钟。精确计算功耗有助于更准确的系统热设计和电源容量规划。

封装与可靠性:3225主流选择

3225 (3.2mm x 2.5mm) 是当前主流封装尺寸。在PCB布局时,应优先将晶振放置在靠近时钟负载的位置。同时需评估厂商提供的长期老化数据(如年老化率)和供应链稳定性。

实战选型流程与避坑指南

关键摘要

- 应用定基调:312.5MHz LVDS晶振是AI加速卡与400G/800G光模块的核心,选型需紧扣同步精度要求。

- 精度是基石:总频差与温度稳定性保障了时钟的长期准确性。

- 相位噪声定上限:低RMS抖动是确保高速SerDes链路低误码率的关键指标。

- LVDS优势:高抗干扰性、低功耗,是高频时钟分配的首选接口。

- 系统化验证:通过PSRR、封装布局及实测验证,确保最终性能锁定。