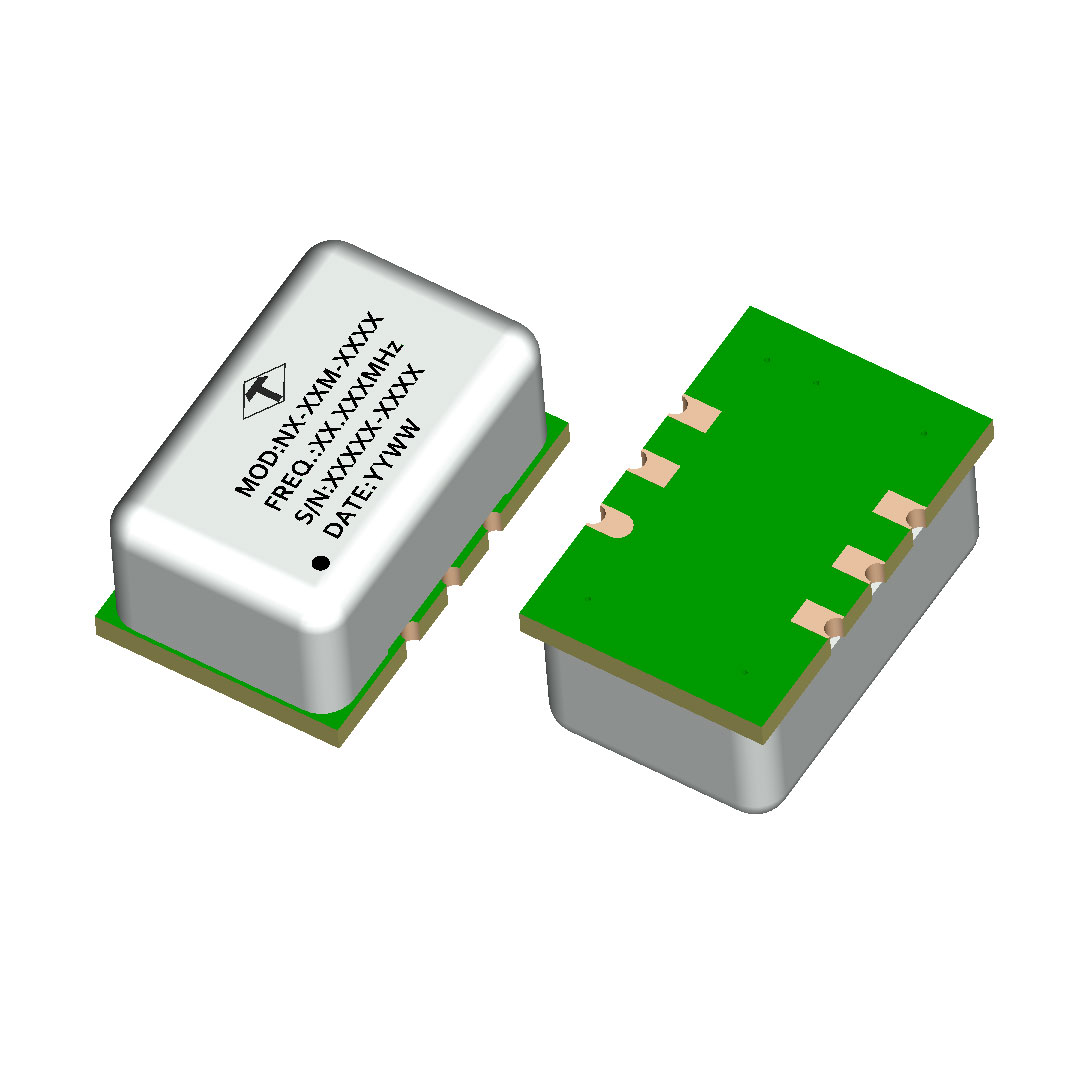

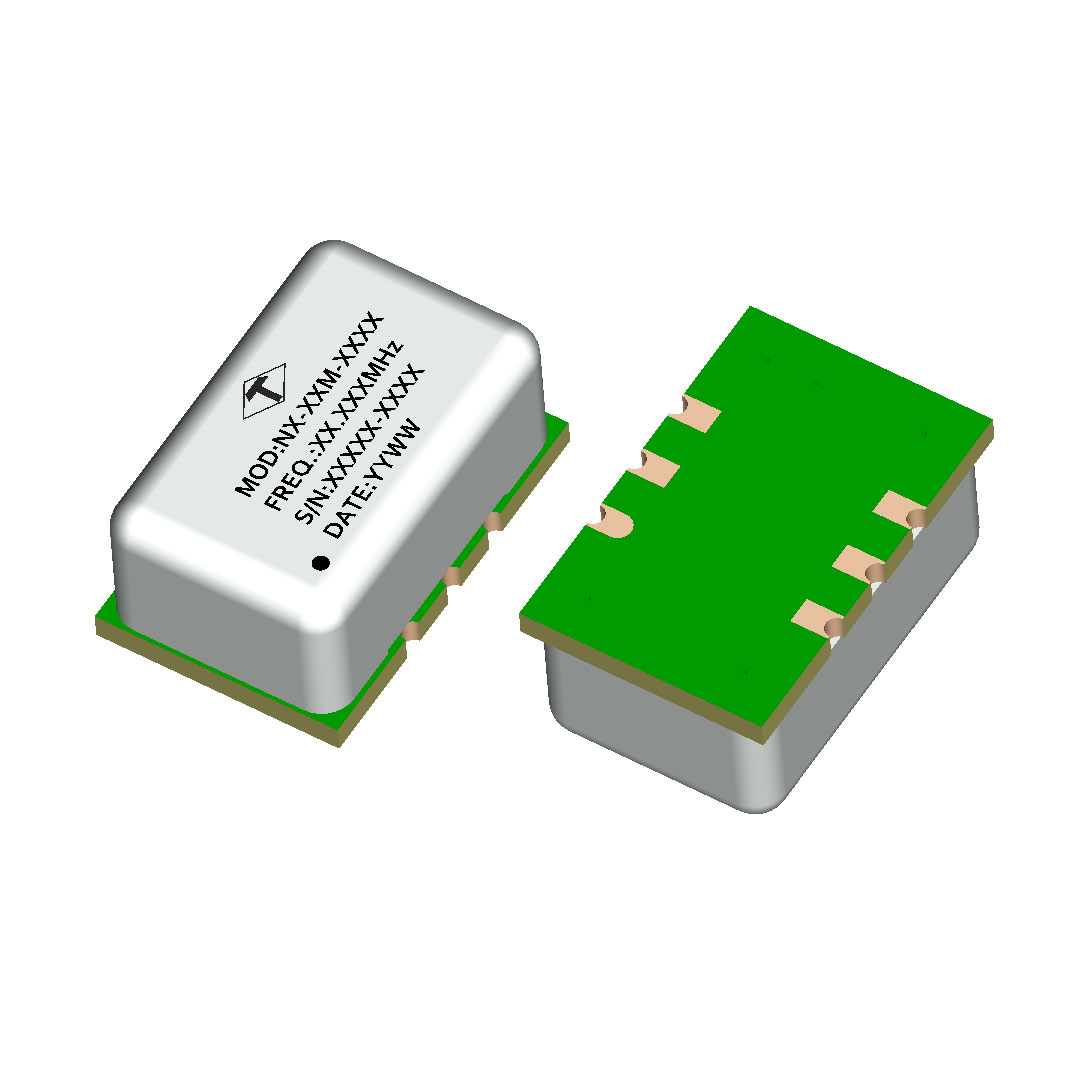

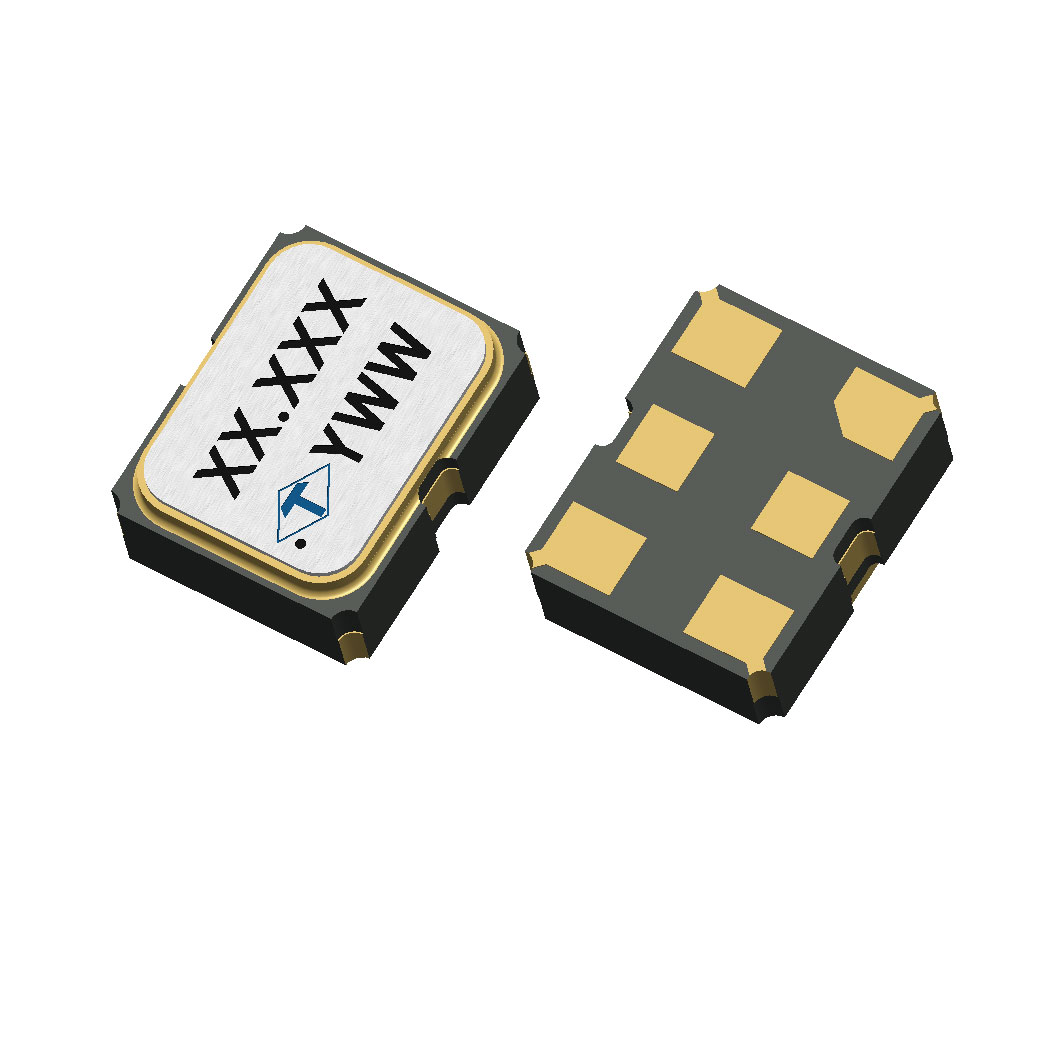

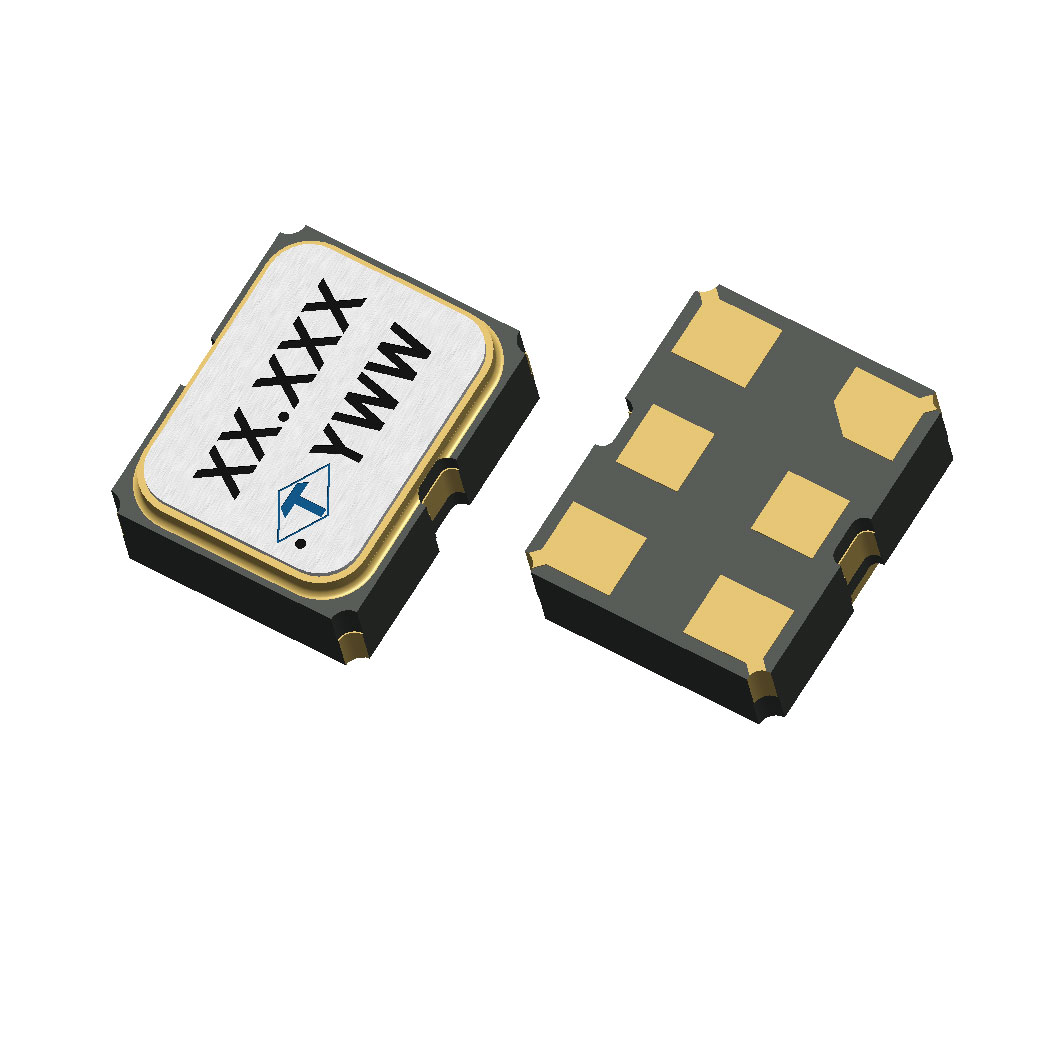

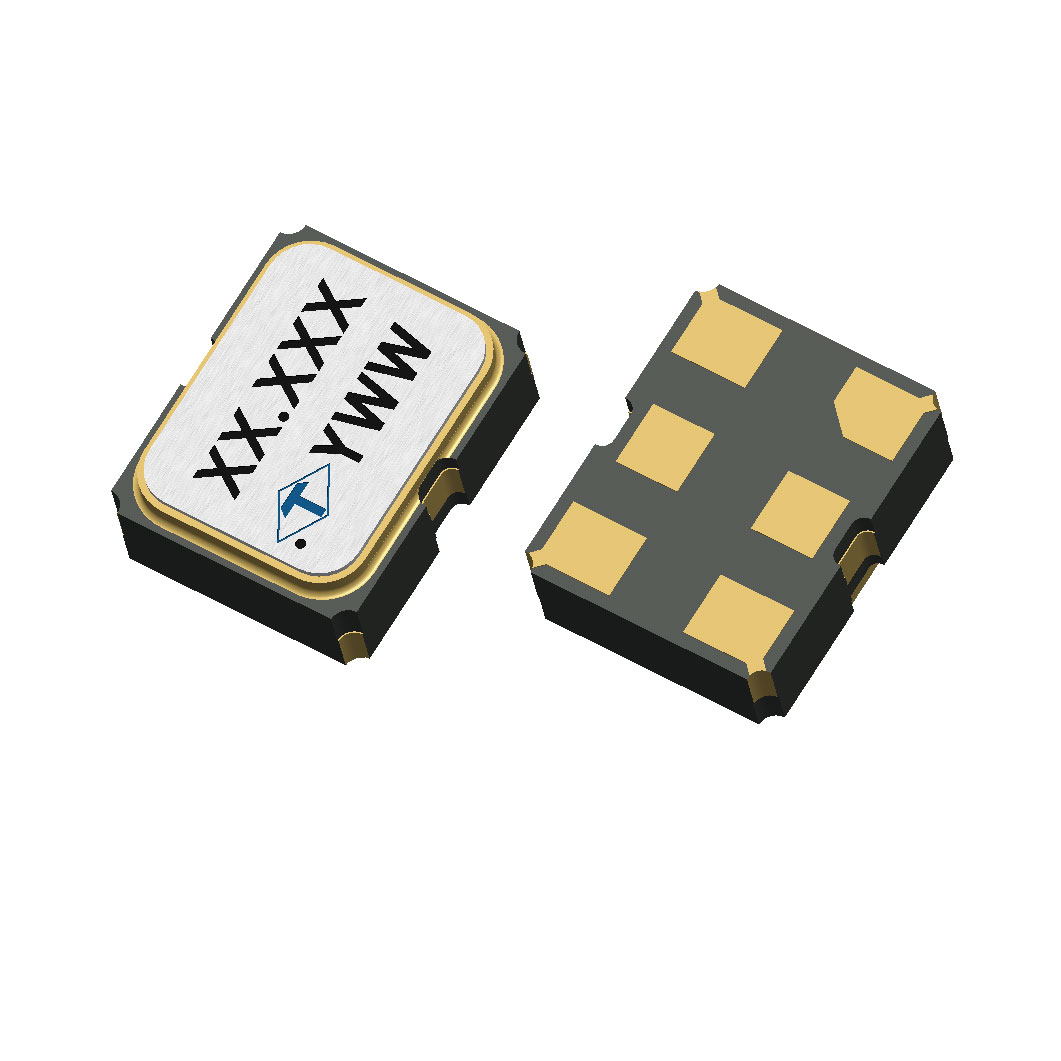

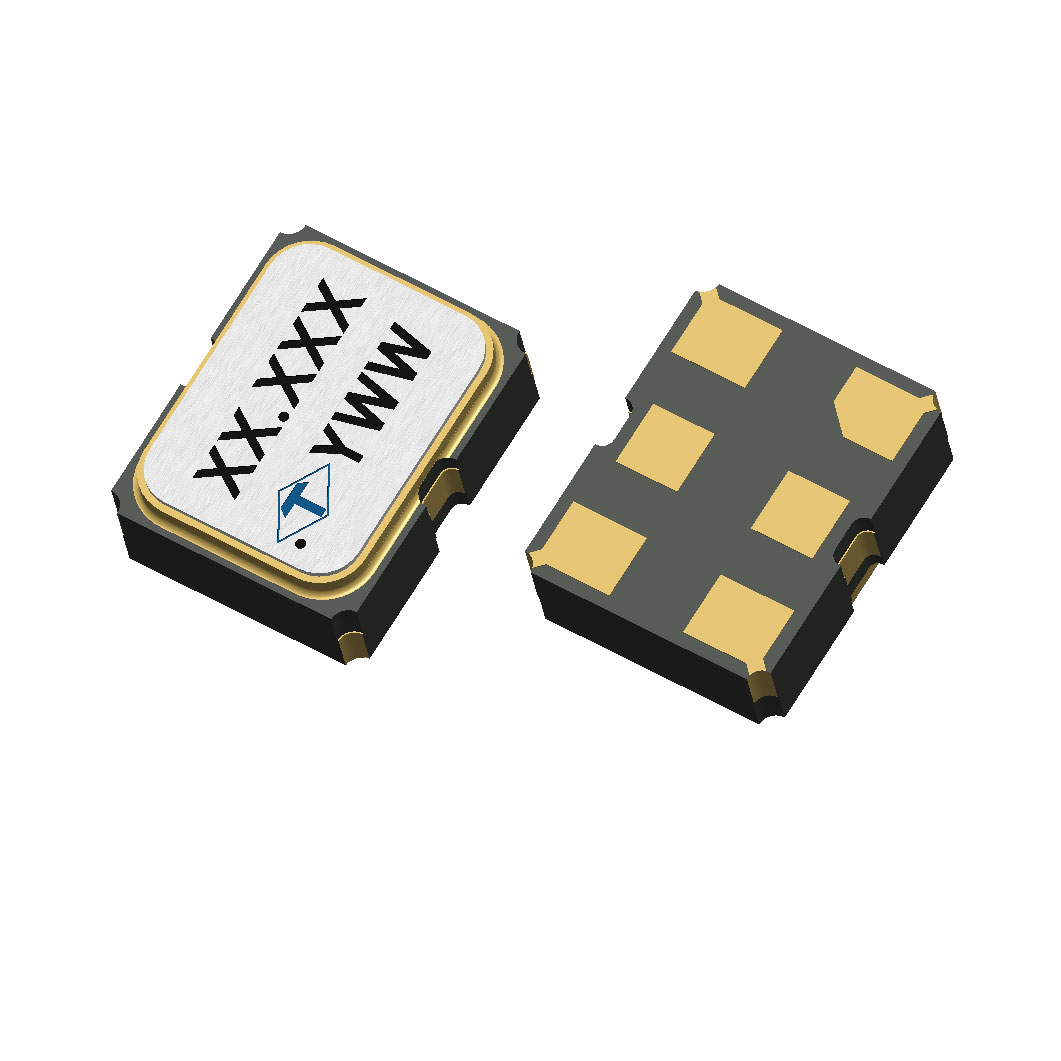

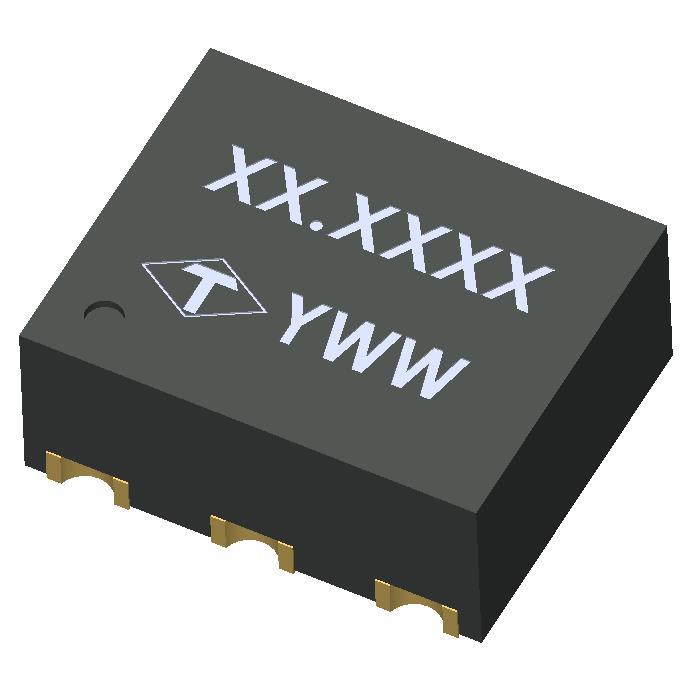

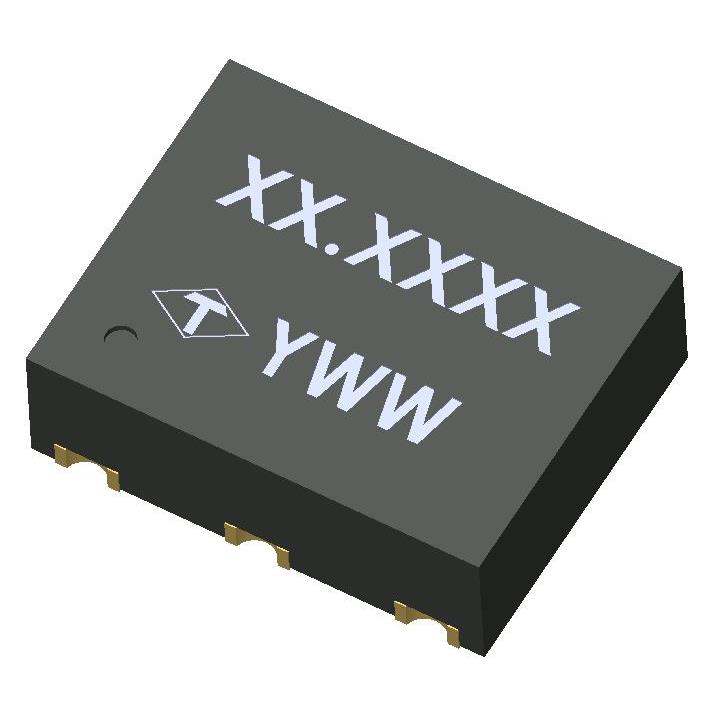

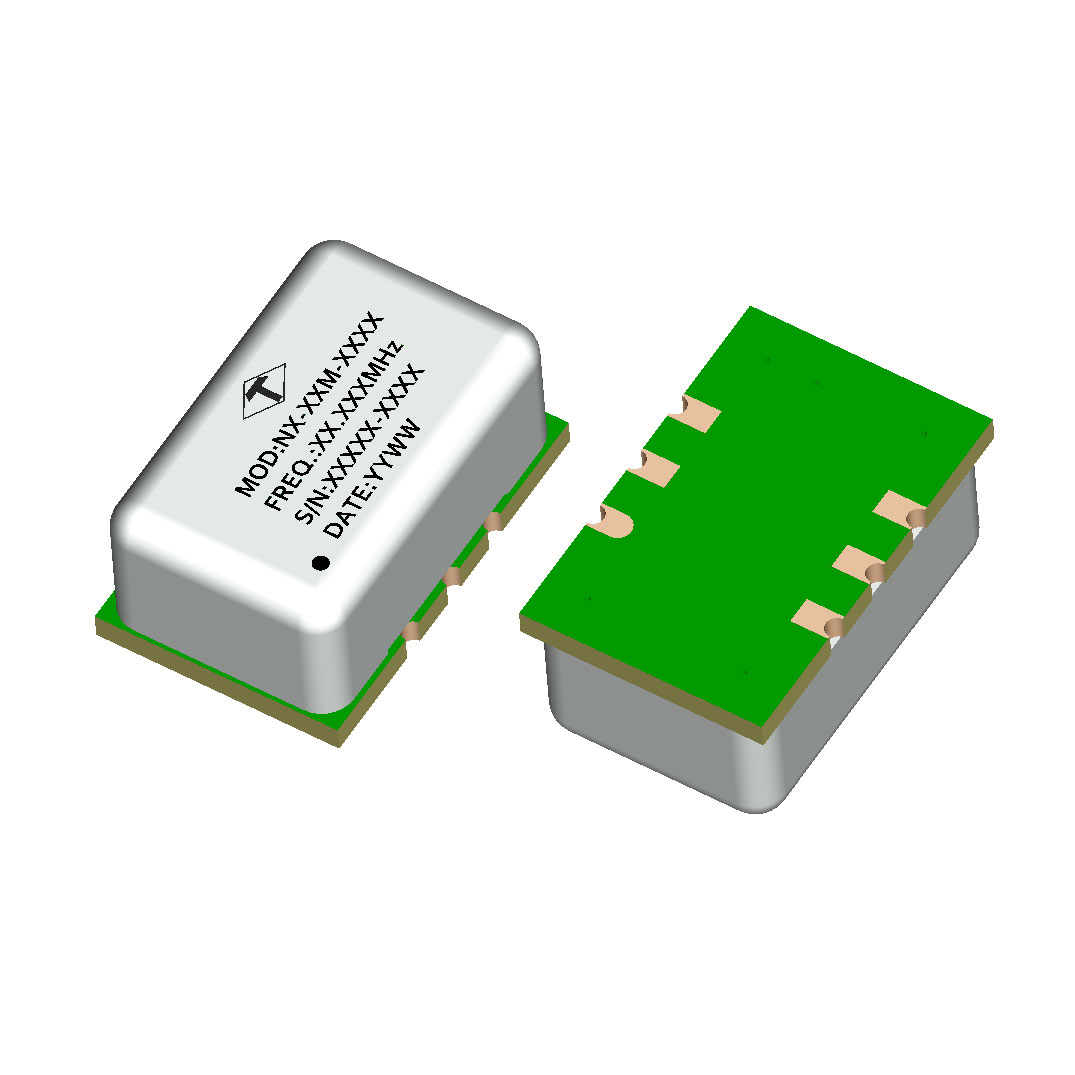

10MHz OCXO 核心参数、2025年市场动态与全球库存深度解析 现货均价: ¥168 温度稳定性: ±10 ppb 国产 NJECBLJHNY-10.000000 在 2025 年 Q2 现货均价已降至 ¥168,较 2024 年同期再跌 11%;而海外渠道仍报 $26–$29。为什么同一颗 10 MHz OCXO 会出现如此价差?本文用一张权威规格书 + 实时库存雷达,帮你锁定最低成本采购窗口。 规格书全景速览:10MHz OCXO 核心参数一次性拆解 图:NJECBLJHNY-10.000000 封装与内部架构示意 NJECBLJHNY-10.000000 以 ±10 ppb 温度稳定性、3.3 V CMOS 输出与 250 mW 典型功耗,成为 2025 年高端恒温晶振的“守门员”。 频率精度 (±50 ppb) 10.000000 MHz 温漂表现 (-40°C~+85°C) ±10 ppb 稳态功耗 250 mW 7-SMD 无铅封装尺寸与焊盘细节图 关键维度 数值指标 设计备注 长 × 宽 × 高 14.2 mm × 9.2 mm × 6.5 mm 标准 7-SMD 封装,脚间距 2.54 mm 焊盘宽度 1.0 mm 建议回流焊峰值温度 ≤ 260 °C 底部散热垫 4.5 mm × 4.5 mm PCB 设计必须接地散热以维持频率稳定 价格行情 2025:现货、期货、阶梯价三重透视 2025 年 7 月最新行情显示,NJECBLJHNY-10.000000 出现“内冷外热”倒挂现象: 国内市场 (深圳/上海) ¥168 – ¥189 大厂批量到货,单批次 > 50 k 颗。若接受散料托盘,单价可再降 ¥5–¥8。 海外市场 (Digi-Key/Mouser) $25 – $29 交期维持 12–14 周,MOQ 2 k。NCNR 条款下可压至 $25.5,但需承担汇率风险。 库存雷达:代理商、贸易商、平台现货地图 深圳前海实时动态 最新批次:2025-WK24 现货数量:18,420 颗 合规性:RoHS 10/10,支持扫码溯源 海外保税仓调货时间表 香港机场仓:0–2 天到深,0% 关税 新加坡仓:3–5 天到深,3% 关税 美国仓:FedEx 优先 7 天,7% 关税 选型指南:如何用这份规格书快速验证设计 稳定性匹配 若系统要求 ±50 ppb,该 OCXO 可直接上岗;若要求 ±2 ppb,需增加数字锁相或热控补偿。 FPGA 直连校验 确认输入阈值为 LVTTL 0.8–2.0 V,且走线长度需 成本压缩实战:BOM 里如何把 OCXO 砍到 ¥150 以下 型号 (同频 10MHz) 稳定度 (Temp) 现货参考价 封装兼容性 NJECBLJHNY-10.000000 ±10 ppb ¥168 7-SMD (14x9mm) TXC 7N-10.000MAAJ-T ±25 ppb ¥142 完全兼容 7-SMD KC2520B-CMOS ±50 ppb ¥128 不兼容 (2.5x2.0mm) 💡 专业技巧: 每年 3 月、9 月为代理商清库存窗口,提前 1 个月下达 PO 锁价,通常可获得 5–7% 的额外折扣。 关键摘要 核心指标:±10 ppb, 3.3 V, 250 mW 价格基准:国产现货 ¥168,海外 $25+ 库存高地:深圳前海、香港、新加坡 设计要点:重点查时钟树与电平兼容 采购建议:3月/9月为议价黄金窗口 防伪:激光码结合二维码 99.7% 正品率 常见问题解答 (FAQ) NJECBLJHNY-10.000000 规格书里最大启动电流是多少? 预热阶段启动电流约为 500 mA,持续时间通常小于 60 秒;进入稳态后会降至 80 mA 左右,非常适合对功耗有一定要求的电池供电系统。 10MHz OCXO 能否直接替换 25 MHz TCXO? 不可直接替换。 频率不匹配会导致后端电路无法锁定。若需更换,必须同步调整系统中的 PLL 分频比,并重新验证环路带宽及相位噪声指标。 为什么同批次价格浮动仍有 ¥3? 这通常源于 包装形式 的差异。卷带包装(Tape & Reel)相比托盘散料(Tray)需要额外的编带加工费及卷轴成本,通常每颗会加收 ¥3 左右。 库存雷达多久更新一次? 我们的库存雷达在每个工作日的 10:00 和 16:00 进行两次数据同步。实时现货误差通常控制在 ±50 颗以内。 如何验证到手芯片为原厂正品? 建议通过扫描外壳上的 激光二维码,并结合规格书中的批次号(Date Code)核对激光丝印。原厂封装的合格率通常达 99.7% 以上。