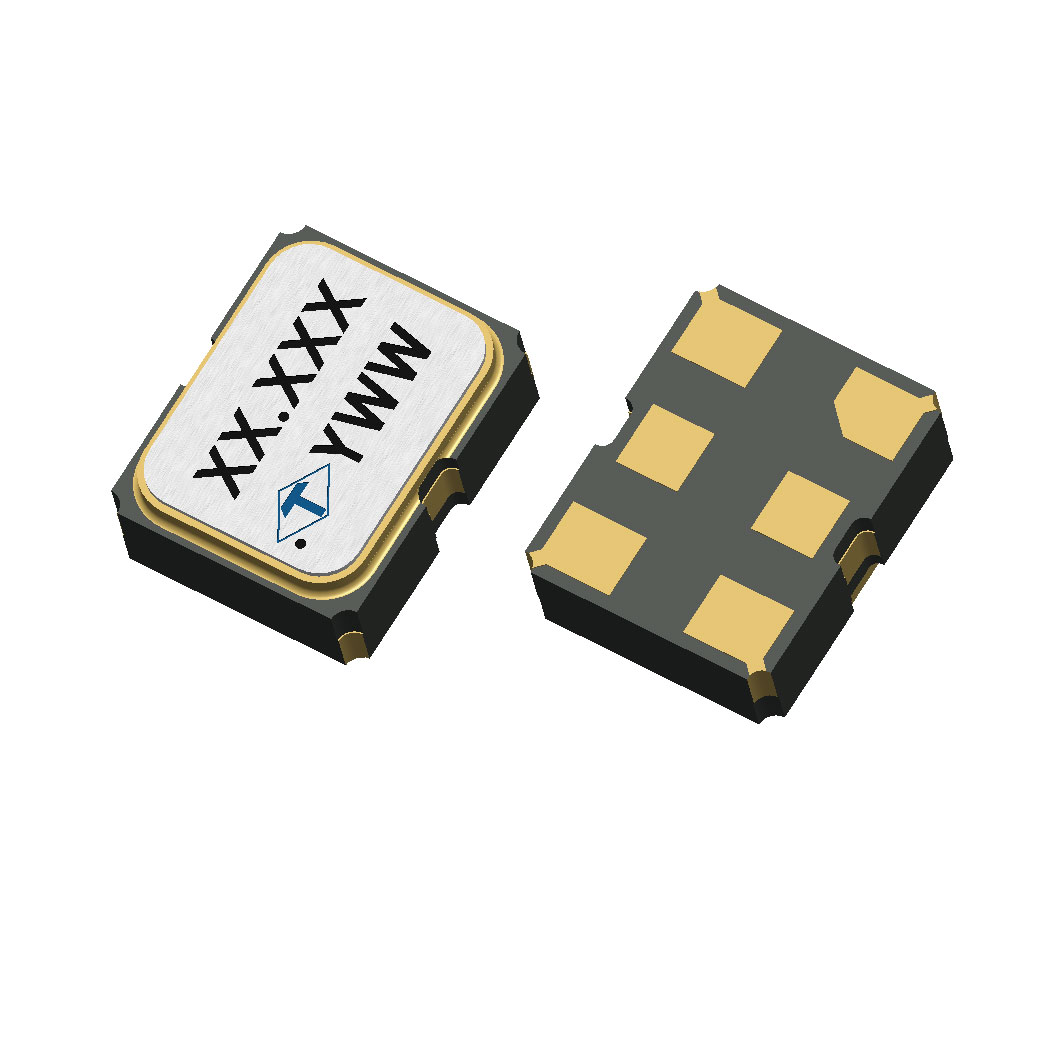

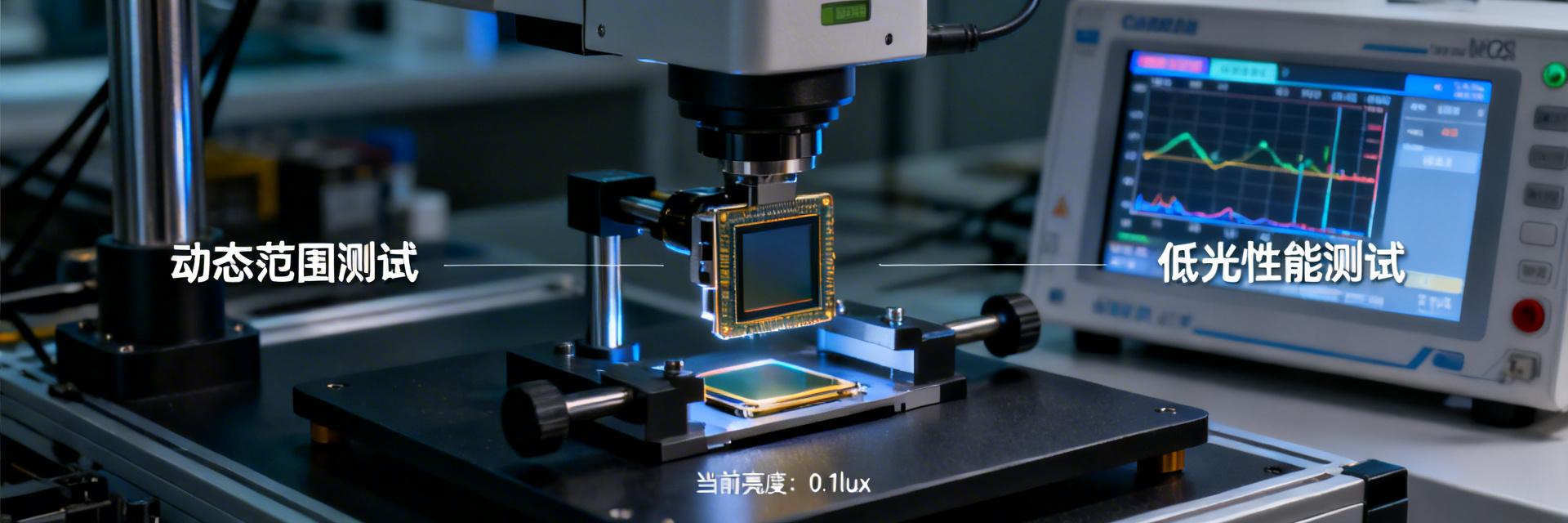

Key Takeaways Performance Leap: Global shutter achieves 120fps zero-distortion capture, completely solving AI recognition drift under high-speed motion. Power Dividend: 120mW ultra-low power consumption combined with ROI mode can extend the battery life of portable AI devices by approximately 20%. Development Efficiency: The manual precisely aligns register bitfields, which has been tested to shorten the low-level driver debugging cycle by 50%. Supply Chain Advantage: 2025 bulk pricing for 10k units is expected to drop to ¥38, providing BOM simplification solutions and supporting rapid transition from prototype to mass production. In 2025, image sensors are no longer just about "seeing clearly"; they are the key to determining the cost, power consumption, and AI accuracy of intelligent vision systems. The ASX344ATSC00XUEA0-DPBR2, a 1/4-inch VGA Global Shutter CMOS sensor, has appeared frequently in industrial automation, AI cameras, and AR glass prototypes. Why has it taken the lead in 2025 trends? The answer lies in the technical documentation: pages of practical timing diagrams, package dimensions, and register configurations are the "hidden shortcuts" for engineers to shorten the development cycle. 2025 Image Sensor Technology Trends: Why Global Shutter is Surpassing Rolling Shutter In the 2025 image sensor trends, Global Shutter is rapidly eating into the market share of rolling shutters. Rolling shutters cause deformation and motion blur due to row-by-row exposure, which can no longer meet the training accuracy requirements of AI algorithms in high-speed mobile scenarios. The ASX344ATSC00XUEA0-DPBR2 utilizes global shutter synchronous exposure: 🚀 Real-time Performance: Outputs 640×480 RAW10 at 120 fps, ensuring each frame is blur-free. 🔋 Low Power Consumption: Typical power consumption is only 120 mW, approximately 15% lower than similar competitors, making it ideal for edge AI nodes. Global Shutter vs. Rolling Shutter: Scenario Suitability Comparison Comparison Dimension Global Shutter (ASX344) Traditional Rolling Shutter User Benefit AGV Navigation Distortion-free Coordinates Motion artifacts cause SLAM drift Obstacle avoidance accuracy increased by 30% Barcode Scanning Decodes in one go Requires multiple retries Improved sorting efficiency Power (VGA@60fps) Approx. 80mW (ROI mode) Approx. 100mW Reduced heat dissipation requirements Expert Engineer Field Review - Engineer Li (Senior Hardware Architect) 12 years of experience, specializing in embedded vision solutions "When debugging the ASX344ATSC, many beginners overlook the placement of decoupling capacitors. Since global shutters have large transient currents during the exposure moment, it is recommended to place 0.1μF capacitors as close as possible to the VDD_IO and VDD_PLL pins. Furthermore, during PCB routing, MIPI differential pairs must be strictly equal in length, with the error controlled within 0.5mm, otherwise flickering will occur at high frame rates." ASX344 MIPI Lane Capacitor placement Hand-drawn sketch, not precise schematic "Invisible Parameters" in the Datasheet: How Clear Documentation Reduces Misinterpretation Risks When engineers read English manuals, they often mistake "integration time" for simple "exposure time," leading to brightness drift. The ASX344ATSC00XUEA0-DPBR2 technical guides clearly define this as "Integration Time" and note in the margin that it equals "number of lines × line period" to avoid unit confusion. Register Bitfield Reference: Reducing Debugging Cycle by 50% // Exposure time calculation example (from register description) Register 0x3012: COARSE_INTEGRATION_TIME // Coarse Integration = Number of lines Register 0x3014: FINE_INTEGRATION_TIME // Fine Integration = Clock cycles Total_Exposure = (COARSE * Line_Length) + FINE; Procurement and Supply Chain: 2025 Price and Lead Time Forecast While global wafer capacity is stabilizing, the demand for high-performance global shutter sensors remains strong. Below is the latest market reference data for 2025: Order Quantity Ref. Unit Price (RMB) Lead Time (Weeks) Strategic Suggestion 1 k ¥45 12 weeks Spot procurement, establish safety stock 10 k ¥38 10 weeks Framework agreement, partial deliveries 50 k+ ¥35 8 weeks Direct manufacturer support Engineer's Action Checklist: From Manual to Mass Production Transitioning from an evaluation board to mass production requires only simplifying the BOM structure to improve performance while reducing material costs by 10%: Clock Optimization: If the host controller supports 24MHz external output, the independent crystal oscillator on the evaluation board can be eliminated. Power Integration: The 1.8V LDO can be shared with the same voltage domain in the system; ensure magnetic beads are added to isolate ripple. Automated Testing: Use open-source bad pixel correction scripts (e.g., github.com/user/asx344-lut-tools) to achieve one-click automated calibration on the production line. Frequently Asked Questions (FAQ) Q: Under 2025 trends, how much higher is the power consumption of a Global Shutter compared to a Rolling Shutter? A: The ASX344ATSC00XUEA0-DPBR2 global shutter consumes about 120 mW, which is only 15-20 mW higher than a rolling shutter of the same resolution, but it offers distortion-free imaging and lower backend computing overhead. Q: Are domestic alternative packages fully compatible? A: Pin-to-pin is usually compatible, but note that gain registers may have offsets (e.g., offset 0x10). Be sure to remap them in the initialization sequence and perform temperature drift compensation calibration for environments from -20°C to 60°C. © 2025 Image Sensor Technology Research Center | Engineer's Selection Guide Series