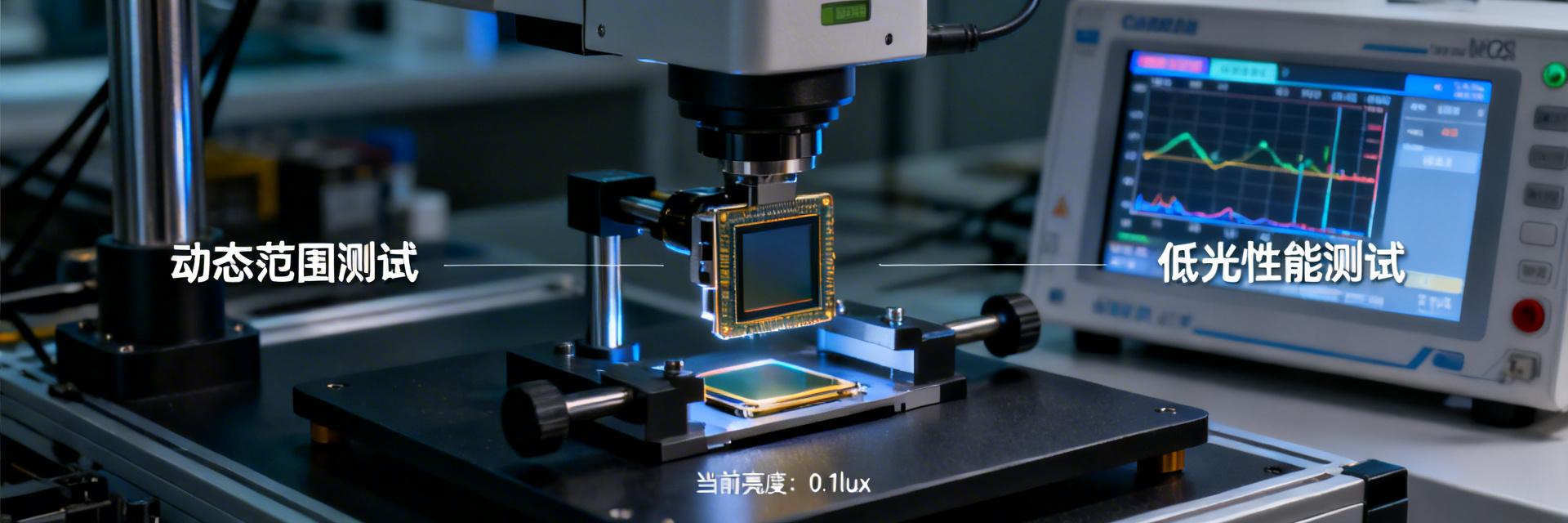

Key Takeaways Architectural Gap: BSI technology places photodiodes above the circuit layer, increasing quantum efficiency by over 30% and directly improving low-light imaging. Performance Balance: 20MP resolution provides high resolution while avoiding power consumption bottlenecks associated with ultra-high pixel counts through a 1.4μm pixel size. Automotive Advantage: Supports Staggered HDR technology, dynamically covering 80dB+ light ratios to solve recognition challenges in high-glare scenarios like tunnel entrances. Integration Essentials: MIPI CSI-2 4-lane interface is standard; designs must strictly control power rail noise to eliminate Fixed Pattern Noise (FPN). Whether your phone captures clear nightscapes in low light or your car accurately identifies road conditions on a rainy night, a high-performance 20MP BSI image sensor is likely working silently behind the scenes. As vision applications expand from consumer electronics into industrial and automotive sectors, choosing and successfully integrating the right 20-megapixel Back-Illuminated sensor for your project has become a core challenge for engineers. This article deconstructs the technical core of 20MP BSI sensors, providing a complete practical guide from selection evaluation to system integration to help you make precise decisions and achieve efficient implementation. Understanding the Core: Technical Advantages and Market Positioning of 20MP BSI Sensors In today's pursuit of higher image quality and complex environmental adaptability, 20-megapixel Back-Illuminated (BSI) sensors are becoming a critical choice for high-end imaging solutions. Their core value lies not in simply stacking pixels, but in finding a sophisticated balance between resolution, light sensitivity, and system power consumption. For engineers, understanding the underlying technical principles is the first step toward making the right selection. Comparison Dimension 20MP BSI Sensor (Mainstream Choice) Traditional FSI Sensor Engineering Advice Quantum Efficiency (QE) >80% (550nm) ~60% BSI significantly improves low-light SNR Pixel Size & SNR 1.4μm maintains high SNR High noise due to wiring obstruction Extends battery life by 10% for the same size Dynamic Range (HDR) Supports Staggered HDR (80dB+) Limited by read noise (~65dB) BSI architecture is mandatory for automotive Package Size Highly integrated, 20% footprint reduction Relatively bulky Ideal for compact ADAS module design Why BSI? The Imaging Revolution of Back-Illuminated Structures In traditional Front-Illuminated (FSI) sensor structures, light must pass through complex metal wiring layers before reaching the photodiode, which causes light to be blocked and reflected, especially as pixels shrink, leading to a severe drop in light efficiency. Back-Illuminated (BSI) technology completely flips this structure: it places the light-sensitive layer above the circuit layer, allowing light to enter the sensitive area directly and without obstruction. This structural innovation brings significant performance improvements: at the same pixel size, the Quantum Efficiency (QE) of BSI sensors is greatly increased, meaning more photons are captured in low-light environments, significantly improving signal-to-noise ratio and dynamic range, laying the physical foundation for high-quality imaging. The Balance of 20 Megapixels: Resolution, Sensitivity, and Power Consumption 20 megapixels is a market-proven "sweet spot" resolution. It provides enough detail for high-definition photography, video recording, and feature extraction in computer vision algorithms, while avoiding the data throughput pressure and power spikes associated with excessively high pixel counts. Specifically, a well-designed 20MP BSI sensor can maintain a moderate pixel size (e.g., 1.0μm or 1.4μm) to ensure single-pixel sensitivity while controlling read noise and power consumption through advanced circuit design and process technology. This makes it suitable for both the extreme image quality pursuits of smartphone main cameras and the rigorous reliability and energy efficiency requirements of automotive systems. Deep Dive into Key Metrics: Selection Evaluation Beyond the Datasheet Faced with complex parameters on a datasheet, engineers need to grasp core metrics that affect system performance for a comprehensive evaluation. These metrics are interrelated and collectively determine the sensor's performance in real-world scenarios. Low-Light Performance and Dynamic Range: Understanding SNR and eDR Modes Low-light performance is paramount when evaluating sensors, and its core quantitative metric is the Signal-to-Noise Ratio (SNR). In low light, a high SNR means cleaner images and less noise. The BSI structure inherently provides an SNR advantage. Furthermore, Dynamic Range (DR) determines the sensor's ability to capture details in both bright and dark areas simultaneously. Many modern sensors support enhanced Dynamic Range (eDR) modes, such as Staggered HDR, which captures images at different exposure times within a single frame and combines them, significantly extending the dynamic range. This is crucial for handling high-contrast environments in automotive scenarios, such as tunnel entrances or oncoming headlights at night. L Lin Jianxun (Senior System Hardware Engineer) Expert Testing and Pitfall Guide "In the PCB layout of 20MP BSI sensors, I've found the most overlooked aspect is decoupling capacitor placement. For the analog power supply (AVDD), capacitors must be placed within 2mm of the pins; otherwise, even with high-spec sensors, the image will show obvious banding noise. Additionally, thermal design directly affects dark current—for every 8°C increase in temperature, the noise level nearly doubles. Automotive applications must include thermal vias." Power Consumption and Frame Rate: Balancing System Efficiency and Real-Time Performance Power consumption directly impacts device battery life and thermal design, while frame rate affects the system's real-time responsiveness. You need to evaluate the maximum frame rate at full resolution and power consumption under different operating modes (such as outputting only a Region of Interest, ROI). For example, in automotive ADAS applications, continuous 20MP full-resolution output at full frame rate may not be necessary; instead, running at a lower resolution for high-frame-rate object detection and triggering full-resolution capture only when needed might be preferred. This flexibility is a key consideration during selection. Interface and Data Throughput: MIPI CSI-2 and Key Interface Considerations High-speed data interfaces are the lifeline for ensuring bottleneck-free transmission of massive image data. MIPI CSI-2 is the de facto standard interface in the mobile and embedded vision fields today. When evaluating, focus on the number of lanes (e.g., 4 lanes), the maximum rate per lane (e.g., 2.5 Gbps/lane), and whether it supports CPHY or DPHY protocols. Sufficient interface bandwidth is a prerequisite for ensuring the sensor works stably at full resolution and high frame rates; otherwise, it will lead to dropped frames or image anomalies. Typical Automotive Vision Integration Architecture 20MP BSI Sensor MIPI CSI-2 (4-Lane) ISP / SoC Processor CAN/Ethernet Vehicle ECU Hand-drawn sketch, not a precise schematic Near-Infrared Enhancement Features: Expanding Automotive and Security Boundaries Many BSI sensors designed for industrial and automotive applications feature Near-Infrared (NIR) enhancement. By optimizing the silicon material's spectral response to the near-infrared band (typically 850nm or 940nm), the sensor can image clearly in total darkness when paired with IR illumination. This feature greatly expands its value in security monitoring, Driver Monitoring Systems (DMS), and night-time autonomous driving perception, serving as a key advantage during selection for specific scenarios. Key Summary BSI Technology is the Foundation: The back-illuminated structure significantly improves quantum efficiency and low-light performance by allowing light to strike the photodiode directly, providing the physical basis for high-quality imaging in 20MP sensors. Balanced Selection is Key: 20 megapixels strikes a balance between resolution and system load. Selection requires a comprehensive evaluation of SNR, dynamic range, power/frame rate, and MIPI interface bandwidth, rather than just pixel count. Scenario-Driven Requirements: Smartphone main cameras seek ultimate image quality and small packaging; automotive vision emphasizes high reliability, wide-temperature operation, and functional safety; industrial inspection focuses on global shutter and special optical adaptation. The application scenario directly drives technical specification choices. Integration Risk Mitigation: Successful integration requires focus on hardware power integrity, clock quality, and thermal design, along with preparation of software drivers, debugging toolchains, and assessment of long-term supply chain stability. Frequently Asked Questions Q1: What are the main differences between a 20MP BSI sensor and a standard FSI sensor in automotive applications? The main difference lies in performance and reliability under low-light conditions. BSI sensors have higher sensitivity, providing clearer images with less noise at night or in tunnels, which is vital for vision-reliant ADAS functions. Furthermore, their superior performance helps reduce reliance on high-power auxiliary lighting, lowering overall system power consumption and heat generation, which better meets the strict reliability requirements of automotive environments. Q2: What are the most common hardware design issues encountered when integrating a 20MP BSI sensor? Common challenges stem from power integrity, clock signal quality, and thermal management. These high-performance sensors typically require multiple core and analog power rails and are very sensitive to voltage noise; improper design can lead to fixed pattern noise or banding in images. High-speed MIPI clock signal integrity is also critical, requiring proper impedance matching and shielding. Additionally, heat generated during high-frame-rate operation must be dissipated through good PCB layout and thermal design to prevent performance degradation due to temperature rise. Q3: How can image output be efficiently debugged for 20MP BSI sensors in resource-constrained embedded projects? A step-by-step debugging strategy is recommended. First, use evaluation boards and companion PC software provided by the sensor manufacturer to confirm the sensor functions correctly and obtain ideal register configurations. Second, on custom hardware, prioritize using an oscilloscope or protocol analyzer to verify that power, reset, and MIPI clock/data signals are correct. Then, start with simple register reads/writes to verify the I2C/SPI control path. Finally, focus on image data reception; you can initially lower the resolution and frame rate to ensure data flow before gradually adjusting to the target mode, using open-source or manufacturer-provided image display tools for real-time viewing. © 2024 High-Performance Vision Technology Column | In-depth Analysis of Sensor Integration Practice