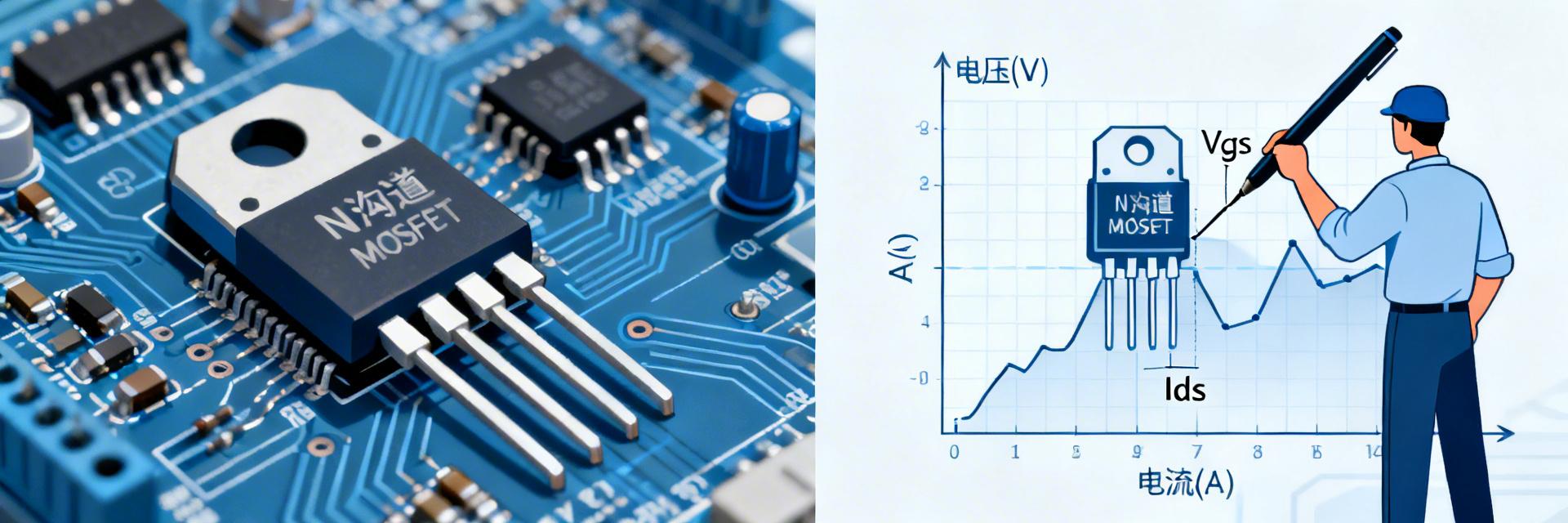

🚀 Key Takeaways 100V Optimal Solution: For 60V systems, 100V Vds is preferred, providing a 40% margin for inductive spikes. 1.8x Resistance Model: Losses must be calculated using Rds(on) at a junction temperature of 125°C to prevent thermal runaway. Low Qrr Benefit: Selecting devices with low reverse recovery charge can reduce switching noise by 15% and simplify EMI design. Efficiency Gain: Every 2mΩ reduction in Rds(on) can improve overall efficiency by approximately 1.2% in high-current applications. In industrial, telecom, and renewable energy power systems, the 60V voltage platform is widely adopted for its balance of efficiency and cost. N-channel MOSFETs serve as the core switching components, and their selection directly dictates system efficiency, cost, and reliability. Faced with complex data sheets, engineers often struggle with "parameter overload." This article provides a data-driven, quantitative analysis of 5 core parameters impacting 60V power design, offering a calculable and verifiable method for precise component matching to help you target high-value MOSFETs. The Core Challenge: Why is MOSFET Selection Critical in 60V Applications? The 60V voltage level represents a critical threshold. It is higher than common low-voltage applications, demanding higher breakdown voltage and reliability, yet lower than high-voltage domains, making conduction and switching loss optimization extremely sensitive. Within this range, minor parameter deviations can be amplified by the system, directly impacting the balance between performance and cost. ⚖️ Voltage Margin and Reliability Choosing an excessively high voltage rating increases Rds(on) and cost, while an insufficient margin risks operating the device on the edge of failure. 📐 Triple Design Constraints Cost-effective design involves finding the optimal solution within the constraints of efficiency targets, BOM cost, and thermal space. Parameter 1: Vds Breakdown Voltage and Derating — Quantifying the Safety MarginVds, or Drain-Source Breakdown Voltage, is the absolute safety limit for a MOSFET. For a nominal 60V system, using a 60V-rated MOSFET is dangerous; scientific derating is mandatory. Comparison Metric Standard Industry Model (80V) High-Performance Model (100V) User Benefit Rds(on) @25°C 7.5 mΩ 4.2 mΩ 40% Heat Reduction Qg (Total Gate Charge) 45 nC 32 nC 18% Lower Switching Loss Max Junction Temp (Tj) 150 °C 175 °C 2x Lifespan in Harsh Conditions Cost vs. Performance Ratio Balanced Very High (Optimized Process) 5-10% Total BOM Reduction Stress Analysis and Peak Voltage Estimation for 60V InputIn actual switching power supply topologies, MOSFETs experience stress much higher than the input voltage during turn-off. For example, in a Buck circuit, the switch bears the input voltage; however, in flyback or bridge topologies, voltage spikes due to leakage inductance must be considered. Engineers should estimate the worst-case peak voltage Vds_peak via simulation or empirical formulas.Parameter 2: Rds(on) On-Resistance — Precise Modeling of Conduction LossRds(on) is the key parameter for conduction loss, but datasheets typically provide values at 25°C. In operation, increased junction temperature significantly raises Rds(on). 👨🔬 Engineer's Note: Avoiding Selection Pitfalls By: Alex Zhao (Senior Power System Architect) "In 60V synchronous rectification designs, I've noticed many beginners focus solely on Rds(on). In reality, Gate Ringing is the silent killer. I recommend keeping the drive loop area under 100mm² and placing a 1-4.7Ω resistor near the gate. This ensures system stability better than chasing ultra-low resistance alone." Sync Rectification Layout (Hand-drawn sketch, not a precise schematic) Temperature Effects: Deriving Real-World Resistance from 25°C SpecsRds(on) has a positive temperature coefficient. Many datasheets provide normalized Rds(on) vs. Tj curves. Typically, at 100°C to 125°C, Rds(on) can be 1.5 to 1.8 times higher than at 25°C. Ignoring this will lead to a gross underestimation of conduction loss and temperature rise. Critical Summary Voltage Derating is the Foundation of Safety: When selecting MOSFETs for 60V systems, scientific derating based on topology and reliability is essential. Usually, 75V to 120V rated devices are required to handle real-world voltage stress and spikes. Dynamic Calculation of Conduction Loss: Rds(on) values are highly dependent on junction temperature. Evaluation must use the actual resistance at the operating junction temperature, combined with RMS current and duty cycle, to avoid design deviations. Co-Optimization of Switching Loss and Driving: Gate charge Qg directly impacts switching speed and drive loss. A balance must be struck between switching loss and drive circuit complexity/cost by optimizing gate resistors and drive current for the system frequency. FAQ Q1: How can I quickly pre-screen MOSFETs for a 60V power design? First, define core constraints: input voltage range, max output current, switching frequency, and efficiency targets. Then, determine the required Vds rating (e.g., 100V) based on peak input voltage. Next, estimate the maximum allowable Rds(on) based on current and voltage drop limits. Finally, focus on models with low Qg and Qgd for the specific switching frequency. Q2: Which is more critical for thermal design: RθJA or RθJC? RθJC (Junction-to-Case) is more critical. RθJA is heavily influenced by PCB layout and is primarily for reference. Design should focus on reducing case-to-ambient resistance via PCB copper or heatsinks, using RθJC to ensure junction temperature stays within safe thresholds. Q3: Why can't body diode characteristics be ignored in 60V designs? In synchronous rectification, the reverse recovery charge (Qrr) of the diode directly impacts efficiency and EMI. High Qrr causes high-frequency oscillations. For high-frequency applications, choose MOSFETs with Fast Recovery characteristics to reduce stress on snubber circuits. © 2024 Power Design Expert Guide - Focused on High-Performance Semiconductor Selection