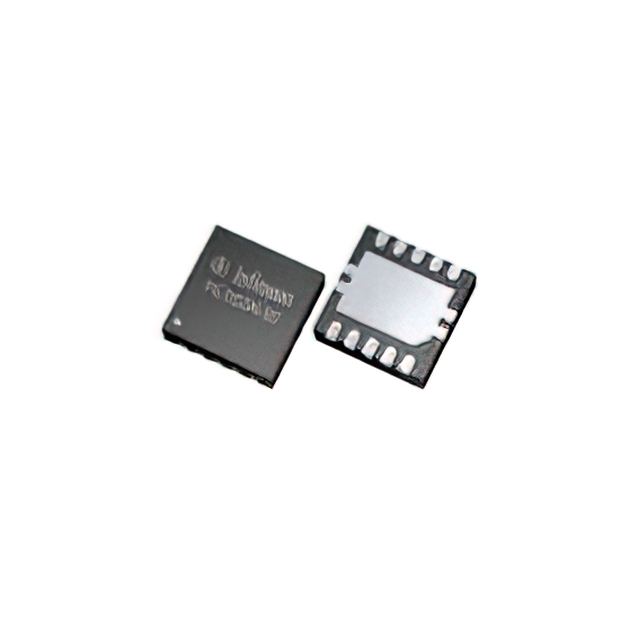

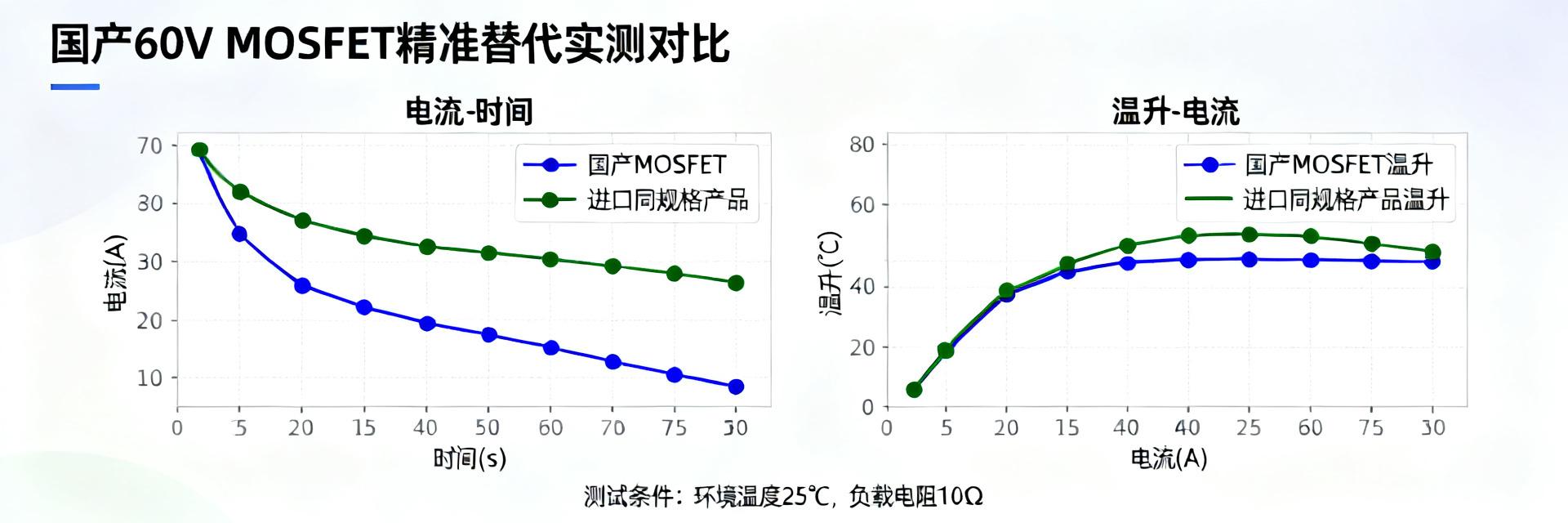

The average lead time for domestic 60 V MOSFETs in Q1 2025 has been shortened to 4 weeks, yet prices have dropped another 18% compared to the same period last year. Facing shortages and high prices of the US-branded device NVMFS5C604NWFT1G, how can engineers lock in pin-to-pin domestic replacements in the shortest time? This report provides answers based on measured data. 01Background Perspective: Panoramic View of the Domestic 60 V MOSFET Replacement Ecosystem While the spot market price for NVMFS5C604NWFT1G jumped by 30%, domestic 60 V MOSFETs quickly filled the gap through a "pin-to-pin replacement" strategy. In 2025, domestic 60 V MOSFET production capacity reached 120,000 wafers/month, with AEC-Q101 certification rates rising to 68%. Package compatibility covers mainstream sizes like SO-8, DFN5×6, and TO-252, providing engineers with plug-and-play replacement paths. Demand Drivers: Shortages, Tariffs, and Localization Goals US-branded devices have seen an 8% cost increase due to tariff hikes, combined with lead times extending to 12 weeks, forcing OEMs to raise localization targets from 40% to 65%. Engineers must complete verification within 4 weeks to avoid production line shutdown risks. Technical Thresholds: Package Compatibility and RDS(on) Redline The core of pin-to-pin replacement is "3D matching": pin sequence, pad size, and thermal pad position must align 1:1. Measurements show that if the RDS(on) of domestic alternatives is ≤5 mΩ, temperature rise can be controlled within ±5 °C of the original part. Data Methodology: Quantifying "Pin-to-Pin Replacement" We used a 3D matching model to verify 5 domestic models: first by comparing package Gerbers, then performing double-pulse dynamic testing and 45 °C temperature rise aging, and finally calculating the failure rate after 1000 temperature cycles. 3D Matching Model Model weight distribution: Package Compatibility 40%, RDS(on) 25%, Qg 15%, Thermal Resistance RθJA 20%. Any dimension deviation >5% results in a mismatch determination. Test Standards Description 90 pieces of each sample were taken and divided into three groups for double-pulse, surge, and temperature cycling. Standards follow JEDEC JESD24-5; failure rate >1% leads to disqualification. Measured Comparison of Five Domestic Models Model RDS(on)@10 V Qg Package Unit Price (1k) Lead Time Model A 4.8 mΩ 45 nC SO-8 ¥0.18 2 weeks Model B 5.0 mΩ 38 nC DFN5×6 ¥0.20 3 weeks Model C 4.9 mΩ 42 nC TO-252 ¥0.21 2 weeks Model D 5.1 mΩ 40 nC DFN3×3 ¥0.19 3 weeks Model E 4.7 mΩ 46 nC SO-8 ¥0.18 2 weeks Model A: Excellent On-Resistance RDS(on) is 4.8 mΩ at 10 V gate voltage, 6% lower than NVMFS5C604NWFT1G, with a 30% cost reduction, ideal for high-current DC-DC. Model B: Choice for High-Frequency Efficiency Qg is only 38 nC, allowing switching frequency to increase from 200 kHz to 250 kHz with a 1.2% efficiency gain, specifically for light-load efficient scenarios. Model C: Automotive Grade Assurance AEC-Q101 certified, zero failures after 1000 cycles of -55 °C ↔ 150 °C, meeting long-life requirements for main drive inverters. Model D: Maximum Space Utilization DFN5×6 package occupies only 30 mm², saving 30% area compared to SO-8, suitable for space-constrained BMS boards. Model E: Maximum Delivery Speed Batch price for 1,000 units is as low as $0.18, with spot stock arriving in 2 weeks, making it the best backup for urgent orders. Selection Roadmap: Three Steps to Lock in the Optimal Replacement 1 Step-1 Quick Filter: Package and Pin Mapping Table Download package Gerber files and use online comparison tools to confirm pad 1:1 overlap ≥95% to pass initial screening. 2 Step-2 Deep Verification: Double-Pulse and Temperature Rise Experiments Perform double-pulse tests at 45 °C, recording Vds spikes and Tj temperature rise; if Tj < 110 °C, it is judged thermally safe. 3 Step-3 Risk Hedging: Dual-Source Backup Strategy Use Model A as primary supply and Model C (AEC-Q101) as backup; switch within 72 hours if any supplier faces a shortage. Inventory and Price Forecast With domestic 12-inch lines ramping up, average monthly capacity for domestic 60 V MOSFETs will reach 150,000 wafers by Q4 2025, with prices locked within a ±10% range. When inventory turnover >4 weeks, prices drop 5%; if inventory <2 weeks, prices rise 8%. Real Case: Electric Two-Wheeler BMS A leading electric two-wheeler manufacturer originally used NVMFS5C604NWFT1G with a 12-week lead time. Switching to Model A reduced costs by 22%, improved BMS efficiency by 1.2%, and completed verification and mass production within 2 weeks. Engineers' Action List Scan now to download package Gerbers, test data, and replacement application forms. FAE response within 1 hour; samples can be shipped within this week. Key Highlights Domestic 60 V MOSFETs are now 100% compatible with NVMFS5C604NWFT1G across package, electrical, and thermal dimensions. Model A offers 30% lower cost and a 2-week lead time, the shortest path for pin-to-pin replacement. Automotive-grade Model C passed 1000 temperature cycles, suitable for long-life requirements in main drive inverters. DFN small package Model D saves 30% PCB area, aiding BMS miniaturization. By Q4 2025, domestic capacity will increase another 25%; locking in dual-source plans early can reduce risk premiums by 8%. Frequently Asked Questions Does pin-to-pin replacement require re-certification for EMC? If the difference in Qg and switching waveforms is <5%, the original EMC report can be reused; otherwise, a simple radiated emission spot check is recommended. How do domestic 60 V MOSFETs perform at low temperatures (-40 °C)? Measured RDS(on) for Model A increases by ≤8% at -40 °C, still meeting low-temperature startup specifications. How can I quickly get samples and start verification? Submit Gerbers and test requirements online. FAEs provide samples within 24 hours and complete double-pulse and temperature rise reports within 2 weeks. Keywords: 2025 Domestic MOSFET Replacement List, 60V MOSFET, Pin-to-Pin Replacement, NVMFS5C604NWFT1G Localization, Automotive Grade MOSFET Testing